Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 1

## **CS-590.26, Spring 2014**

# High Speed Memory Systems: Architecture and Performance Analysis

Alternative Solid State Memories: Flash, MRAM, FeRAM, PCRAM

#### Credit where credit is due:

Slides contain original artwork (© Jacob, Wang 2005)

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 2

### What is DRAM?

- (Relatively) fast reads and (relatively) fast writes

- Unlimited number of writes

- Volatile loses data storage without power

- Dynamic loses data without periodic refresh

- Could be fabricated using similar materials and (relatively) similar silicon based process technologies as leading edge processors

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 3

#### **Alternatives:**

- (Relatively) slower reads and (on some) really slow writes

- (Some) limited number of writes

- Non-Volatile keeps data storage without power

- May require new materials and (relatively) different process technologies as leading edge processors

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 4

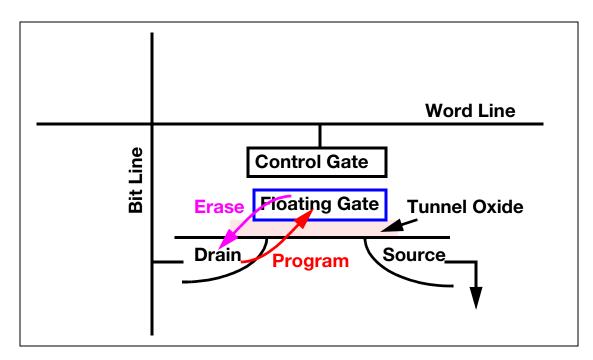

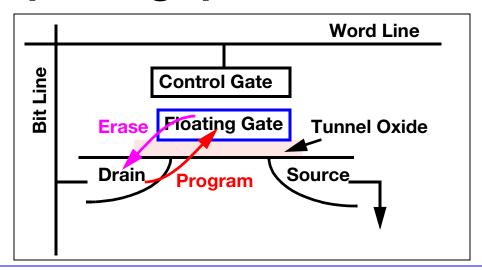

## Flash: Basic Idea

- Electrical charges are forced to tunnel through oxides and get trapped in the floating gate.

- High voltage forces tunneling

- Trapped charges in floating gate then alters V<sub>t</sub>

- Differences in V<sub>t</sub> of transistor then sensed as 0/1

- Explicit program and erase cycles

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 5

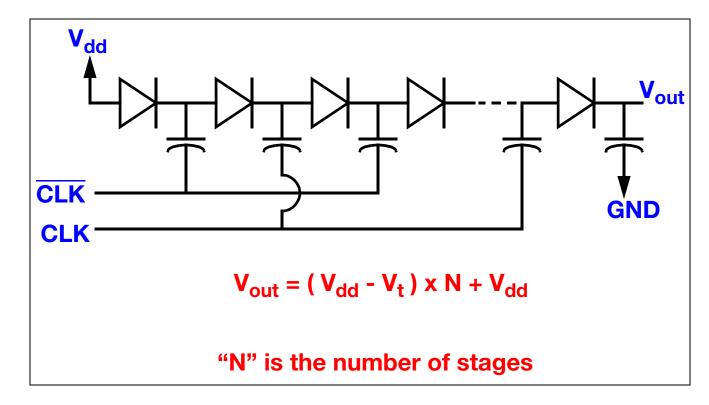

# **Charge Pump**

Idealized charge pumping circuit

- Build up larger voltage for programming floating gate

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 6

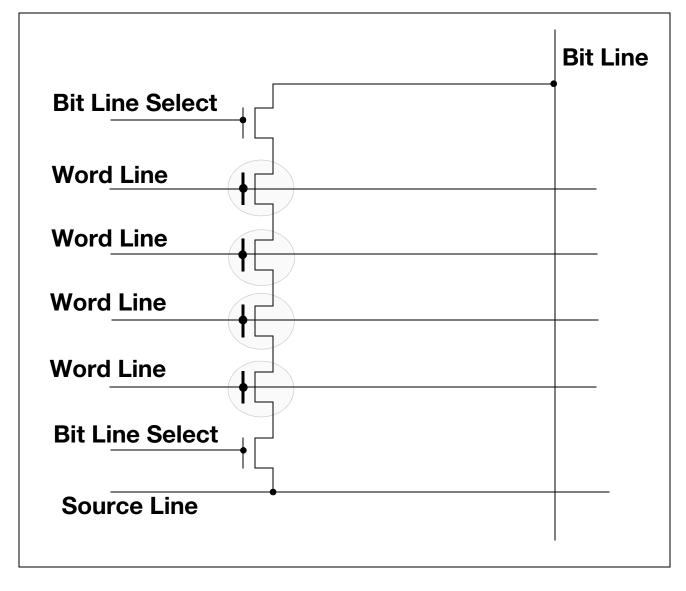

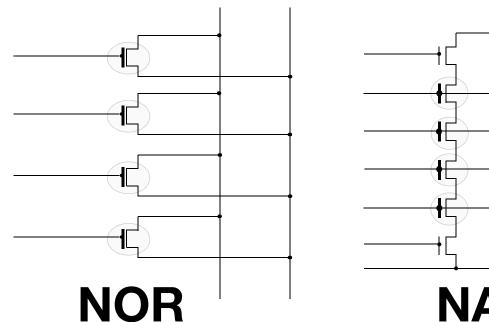

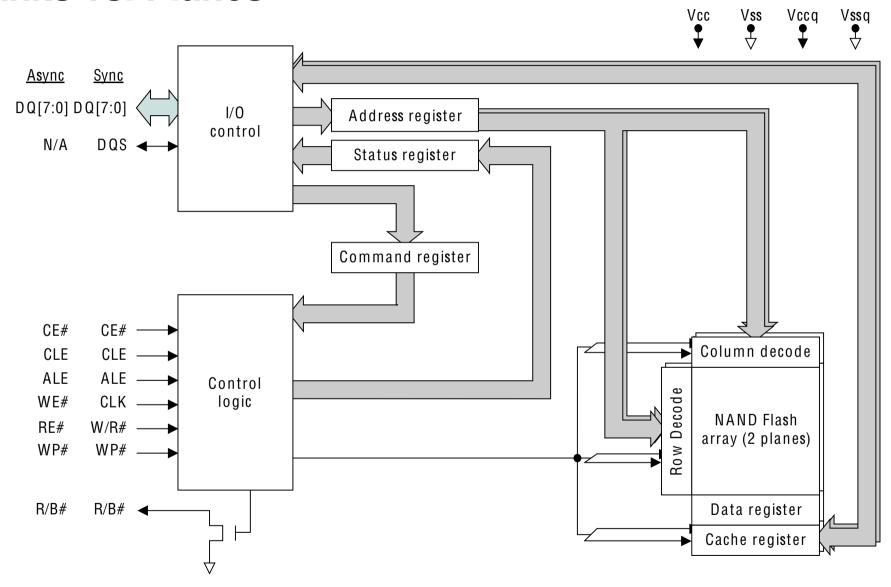

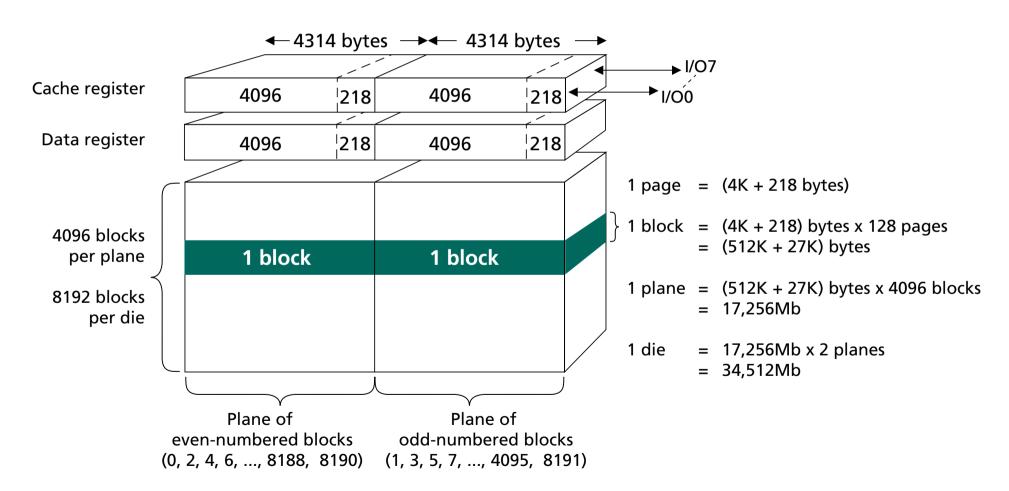

# **NAND Flash Array**

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 7

# UNIVERSITY OF MARYLAND

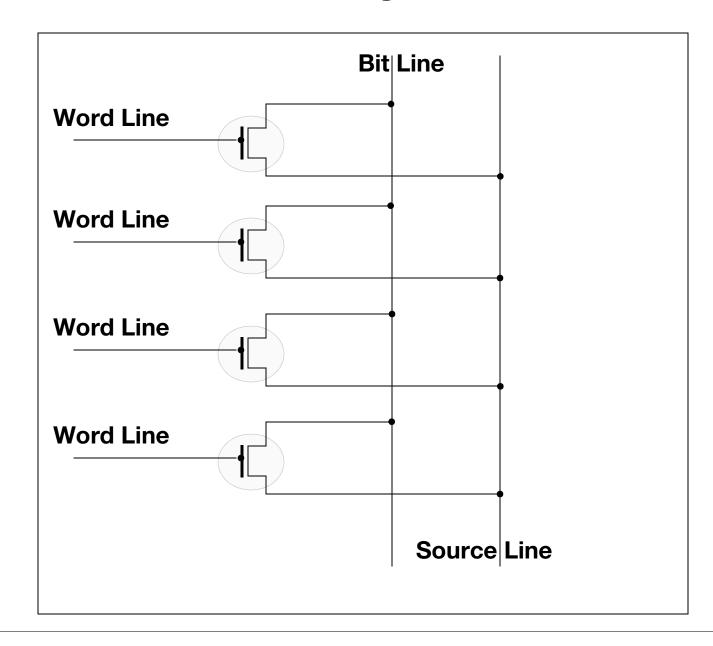

# **NOR Flash Array**

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

> University of Crete

> > SLIDE 8

## NAND versus NOR

NAND **Smaller Cell Size**

**Better E/W Endurance** (>100K vs >10K)

$(\sim 40\%)$

Fast Read (~100ns) Slow Write (~10 us) **Used for Code**

Slow Read (~1 us) "Fast" Write (~1 us) **Used for Data**

\*\*\* values accurate as of 2003 ... updated table in a moment

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 9

UNIVERSITY OF MARYLAND

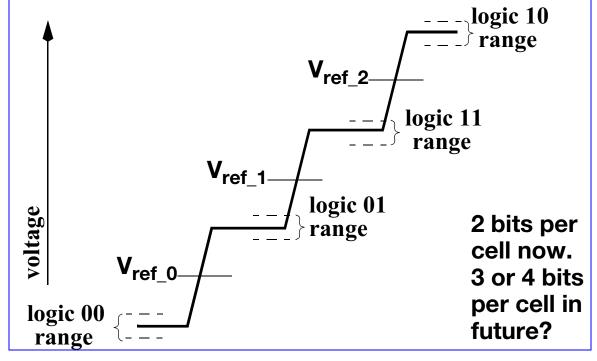

# Multi (voltage) Level Cell

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 10

#### **Reads and Writes**

- Reads are relatively straightforward

- Writes are complex

- How long do we hold the reverse bias currents to "erase"?

- Did the cells erase properly?

- Did the write succeed?

- If the write failed, recover, remap and re-write to another sector/block

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 11

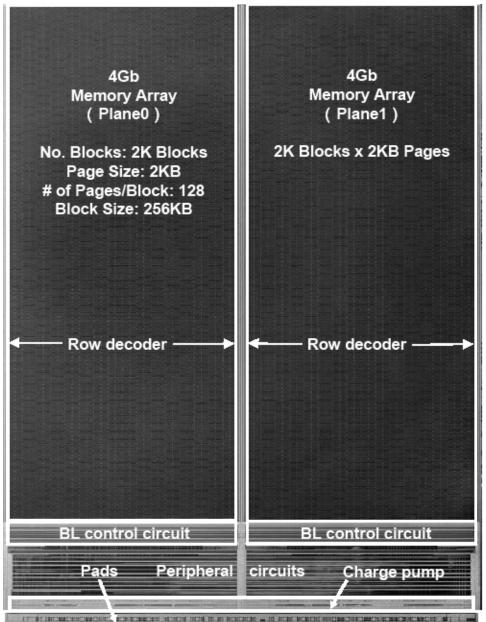

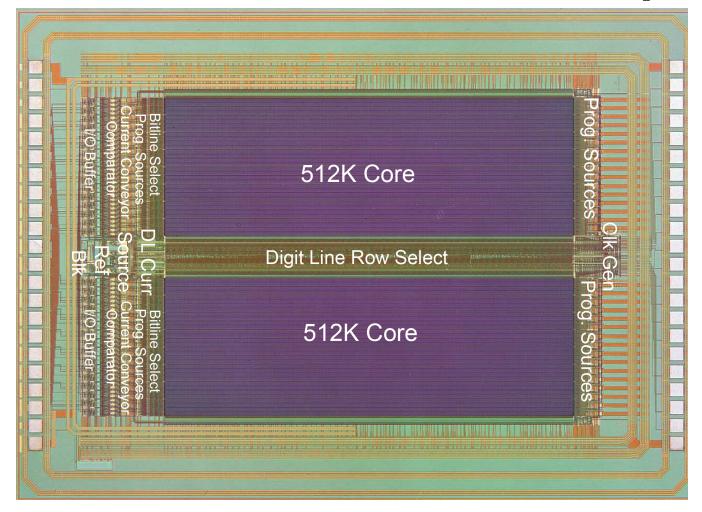

#### **ISSCC 2005: Toshiba 8 Gb NAND**

die size: 146 mm<sup>2</sup>

70 nm CMOS

3M (2AI, 1 W)

cell size: 0.024um<sup>2</sup>

(5 F<sup>2</sup>)

2 bits per cell cycle time: 50ns

program time: 670us

programming

throughput: 6 MB/s

#### Banks vs. Planes

#### Banks vs. Planes

Figure 8: Array Organization: 32Gb and 64Gb Devices

DISK & FLASH

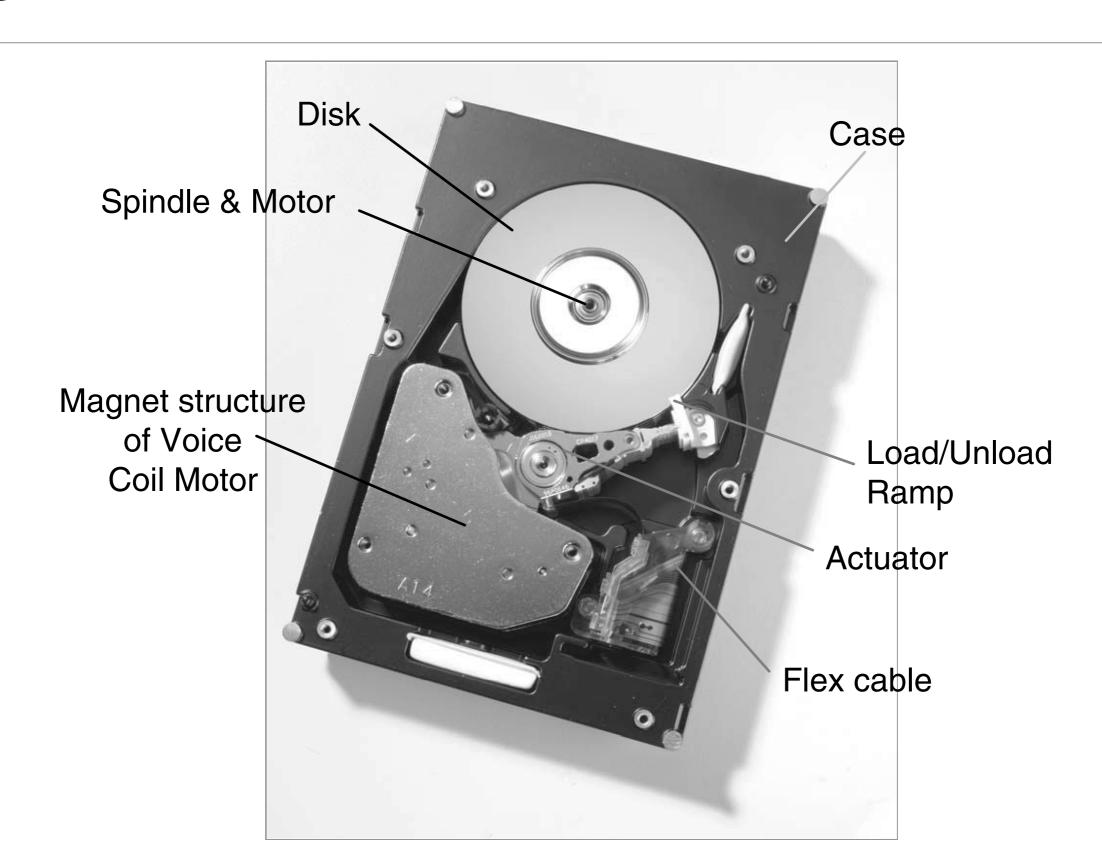

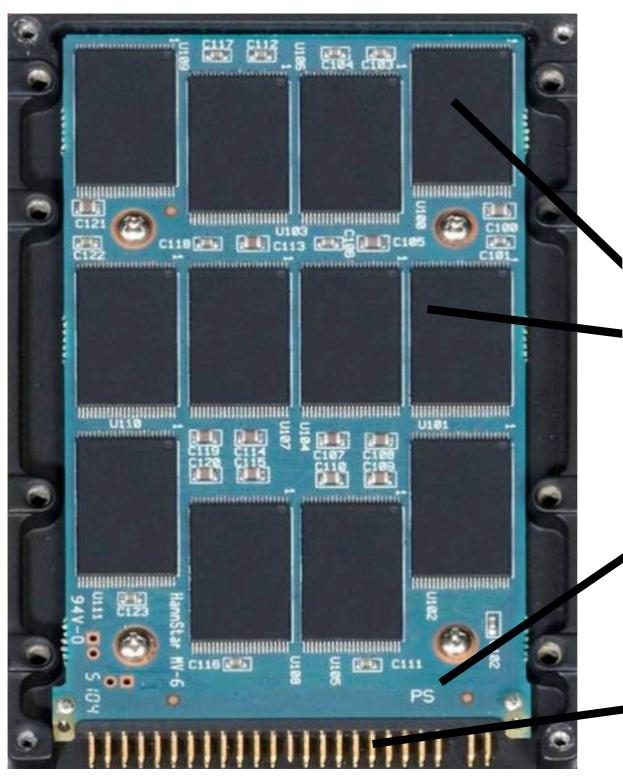

# A brief interlude

# Disk

# Flash SSD

Flash memory arrays

Circuit board

ATA Interface

## Disk Issues

- Keeping ahead of Flash in price-per-GB is difficult (and expensive)

- Dealing with timing in a polar-coordinate system is non-trivial

- OS schedules disk requests to optimize both linear & rotational latencies;

ideally, OS should not have to become involved at that level

- Tolerating long-latency operations creates fun problems

- E.g., block-fill not atomic; must reserve buffer for duration; Belady's MIN designed for disks & thus does not consider incoming block in analysis

- Internal cache & prefetch mechanisms are slightly behind the times

## Flash SSD Issues

- Flash does not allow in-place update of data (must block-erase first); implication is significant amount of garbage collection & storage management

- Asymmetric read [1x] & program times [10x] (plus erase time [100x])

- Proprietary firmware (heavily IP-oriented, not public, little published)

- Lack of models: timing/performance & power, notably

Flash Translation Layer is a black box (both good & bad)

Ditto with garbage collection heuristics, wear leveling, ECC, etc.

- Result: poorly researched (potentially?)

E.g., heuristics? how to best organize concurrency? etc.

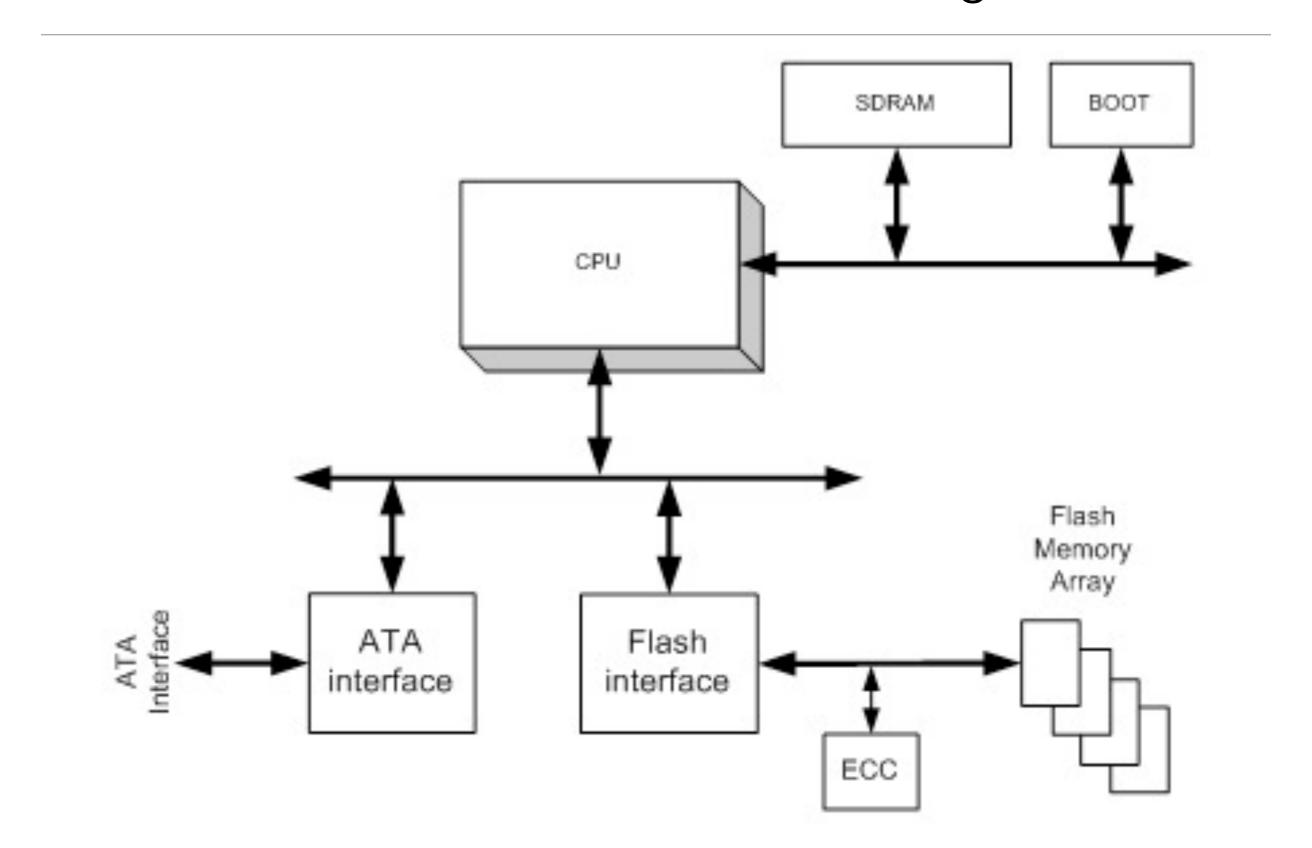

# SanDisk SSD Ultra ATA 2.5" Block Diagram

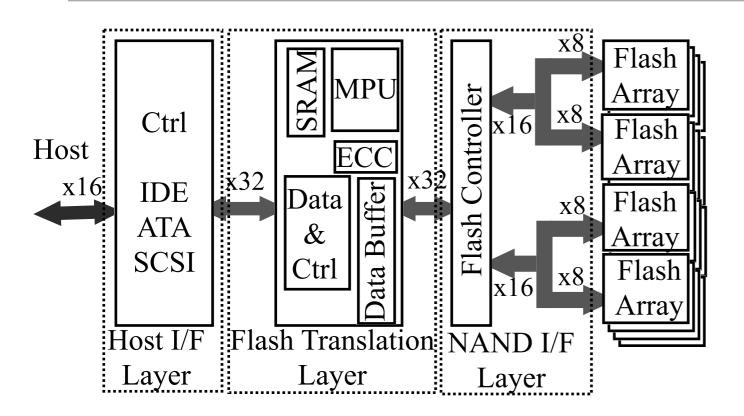

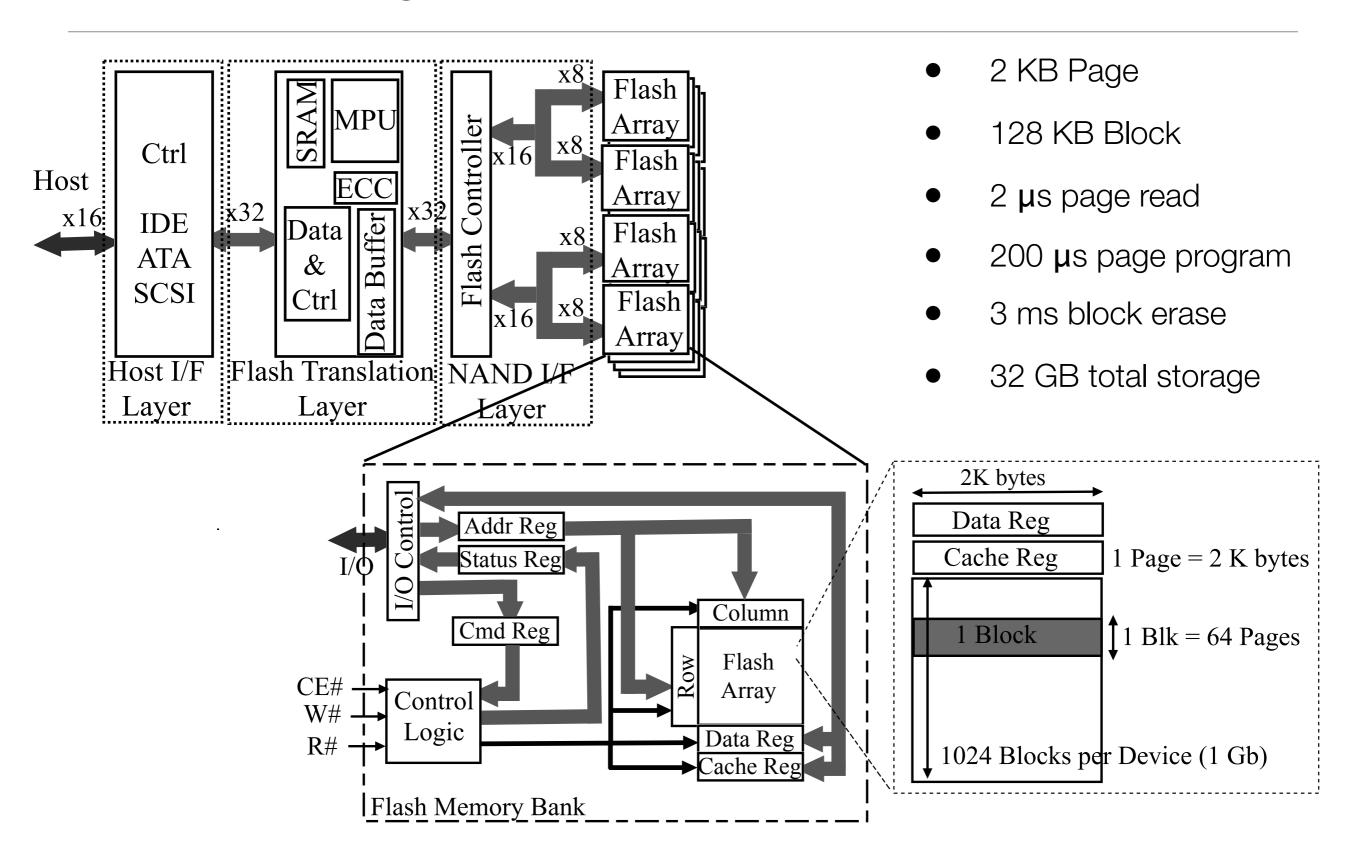

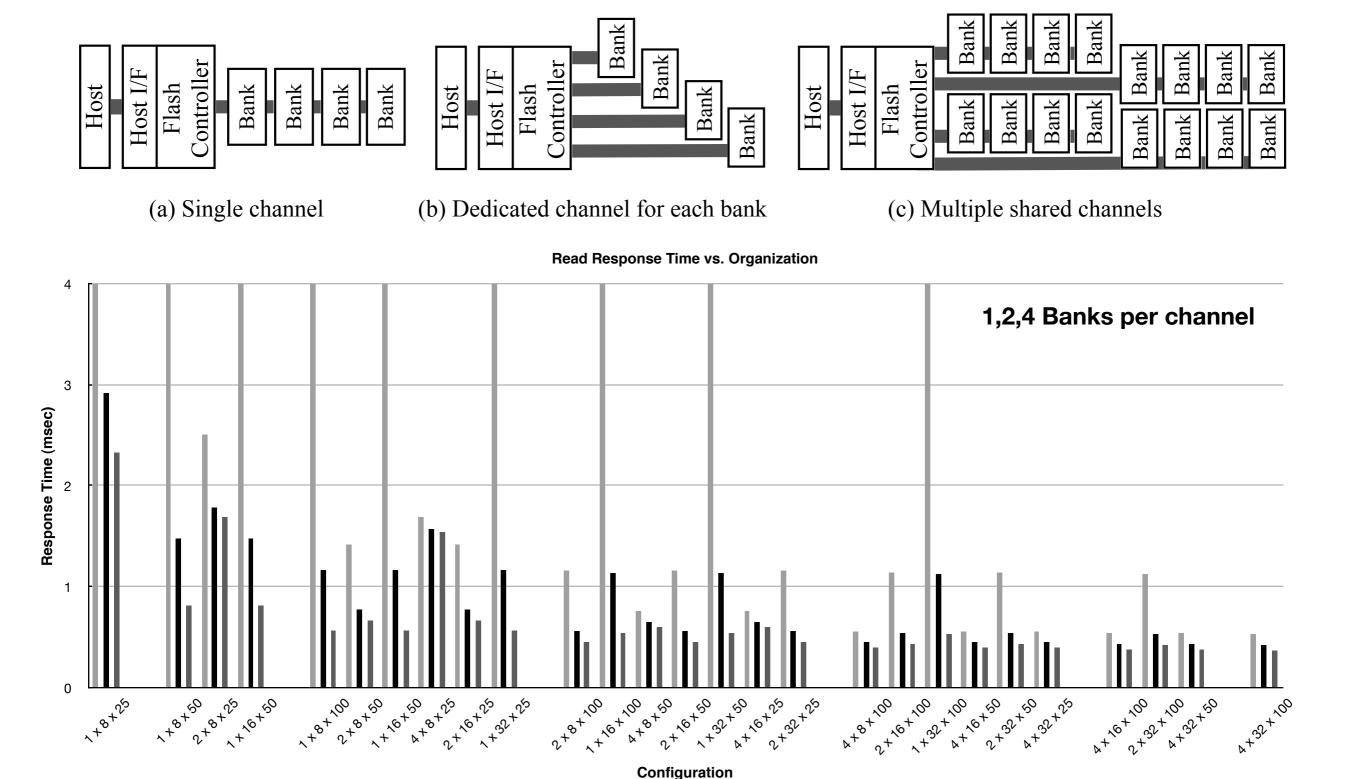

# Flash SSD Organization & Operation

- Numerous Flash arrays

- Arrays controlled externally (controller rel. simple, but can stripe or interleave requests)

- Ganging is device-specific

- FTL manages mapping (VM), ECC, scheduling, wear leveling, data movement

- Host interface emulates HDD

# Flash SSD Organization & Operation

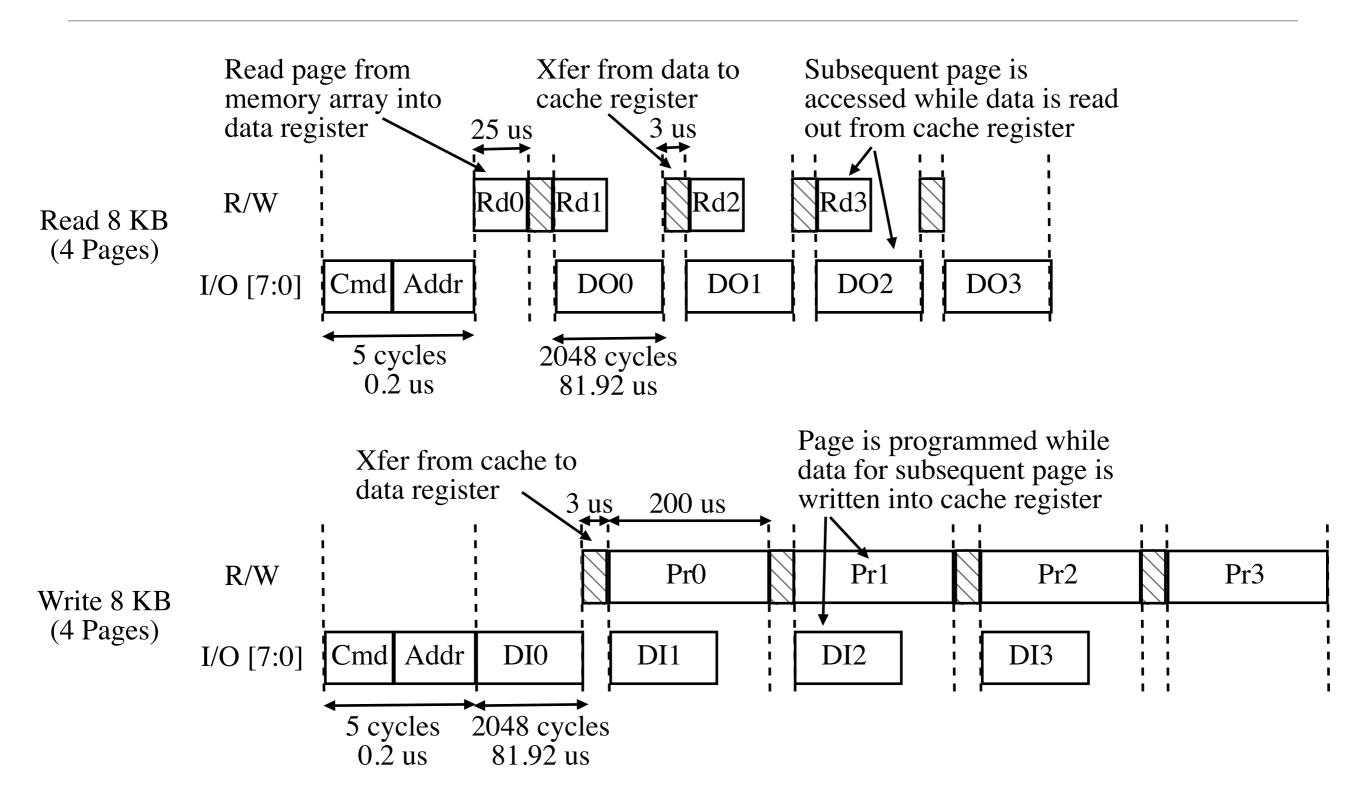

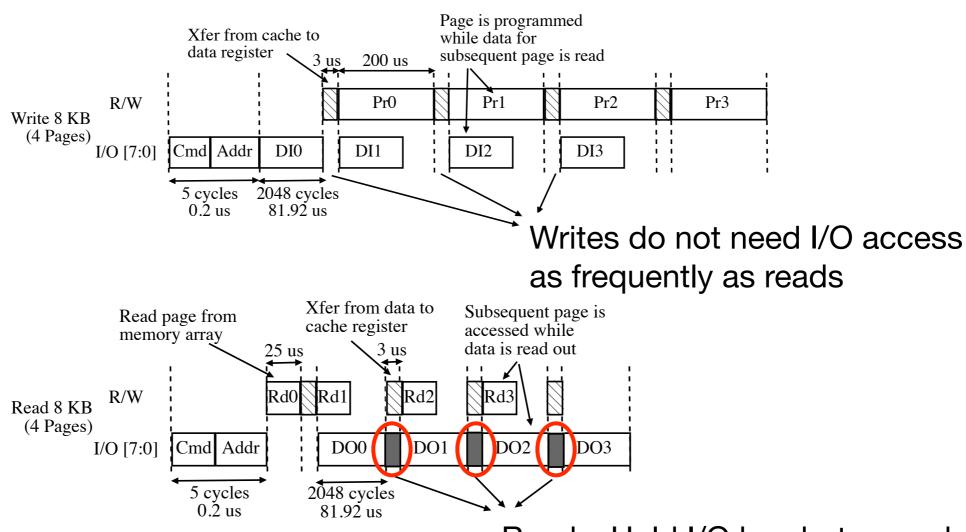

# Flash SSD Timing

## Some Performance Studies

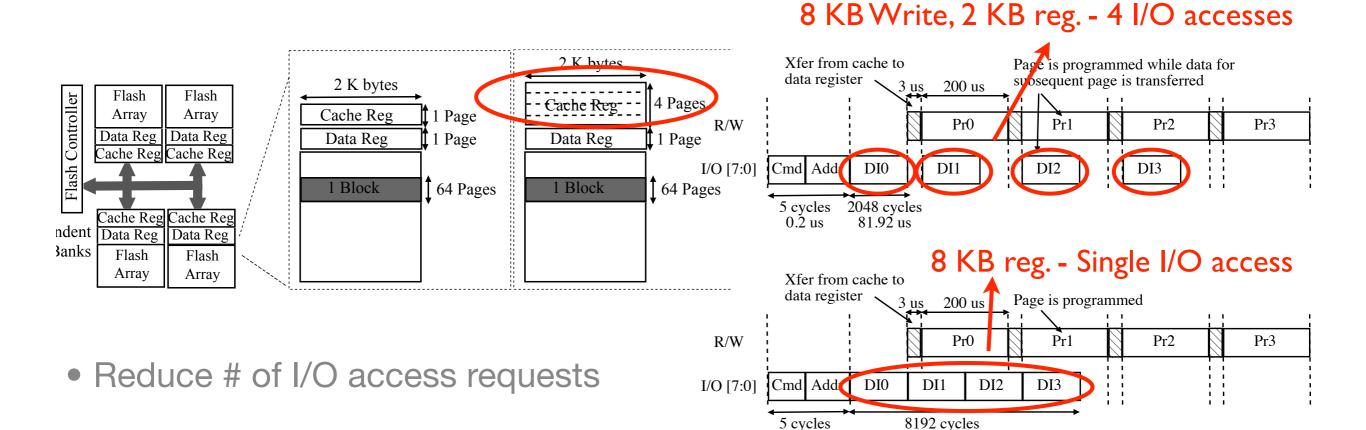

# I/O Access Optimization

- Access time increasing with level of banking on single channel

- Increase cache register size

0.2 us

327.68 us

# I/O Access Optimization

Implement different bus-access policies for reads and writes

Reads: Hold I/O bus between data bursts

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 12

# Generation 2Gb # Blocks 2048 Block Size 128KB

**Parameter**

Page Size

Pages/Blk

Planes/Dies

+ECC

Flash Evolution

2004

**SLC**

2KB

+64

64

1/1

2Gb 32Gb 3 2048 8192

128KB

2KB

+64

64

1/1

2007

**SLC**

8192 4096 512KB 1MB

2008

**MLC**

4KB

1MB

2010

SLC

32Gb

8KB 8KB

2010

**MLC**

128Gb

8192

2MB

+218 +448 +448

128 128 256

2/4 2/1 2/2

Read Time 25µs 25µs 50µs 35µs 75µs

Write Time 300µs 300µs 900µs 350µs 1600µs

Erase Time 2000µs 2000µs 3000µs 1500µs 5000µs

Longevity 100K 10K 10K 60K 30K

Max BW 33MT/s 40MT/s 50MT/s 200MT/s 200MT/s

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 13

## Flash Summary

- Comparable read latency (to DRAM) and slow writes

- Non Volatile

- limited write cycles

- Very mature industry

- Very high density, but long term scalability? Oxide reliability, multi-level cell.

- Video applications now supported

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 14

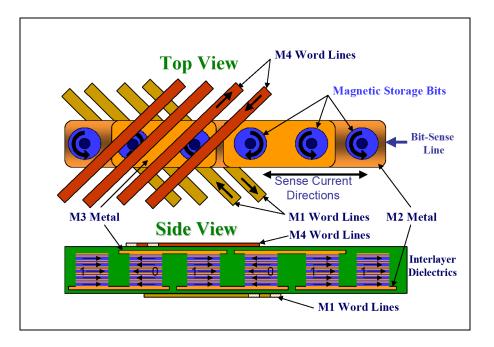

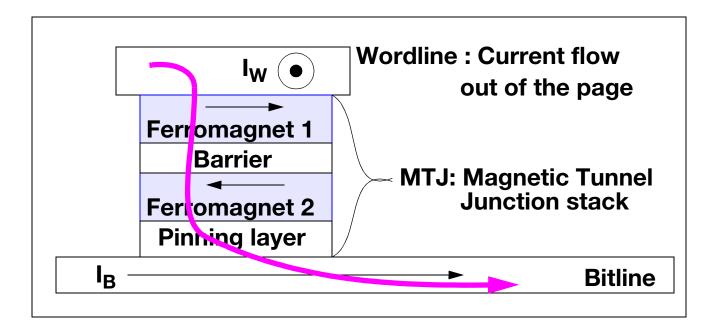

### **MRAM**

#### **MRAM Memory Cell Structure**

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 15

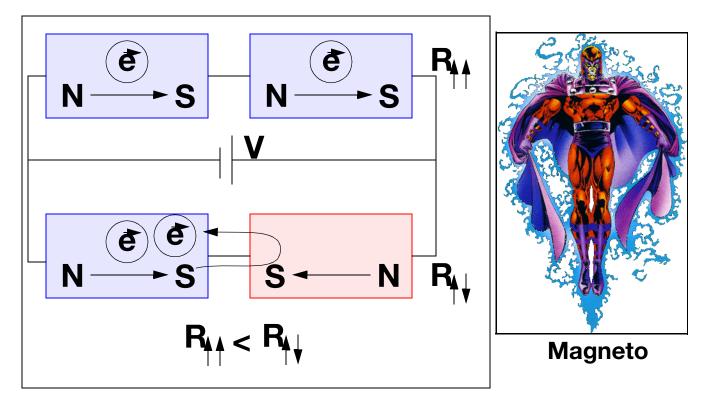

## Magnetoresistance

- Change in electrical resistance with applied magnetic field

The resistance against the flow of electrons depend on polarization of electrons and availability of spin-up or spin-down states

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 16

### **MRAM Cell Structure**

Differences in resistance = "0" or "1"

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 17

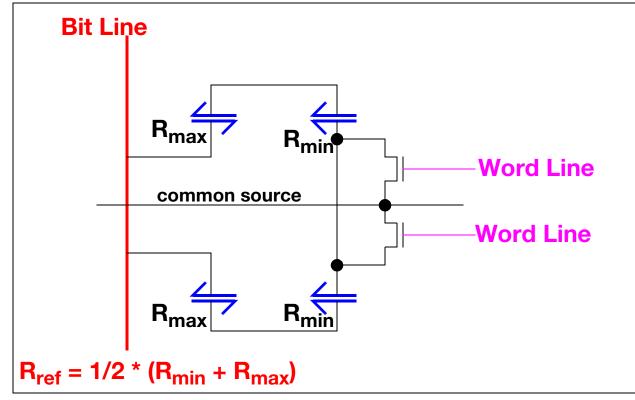

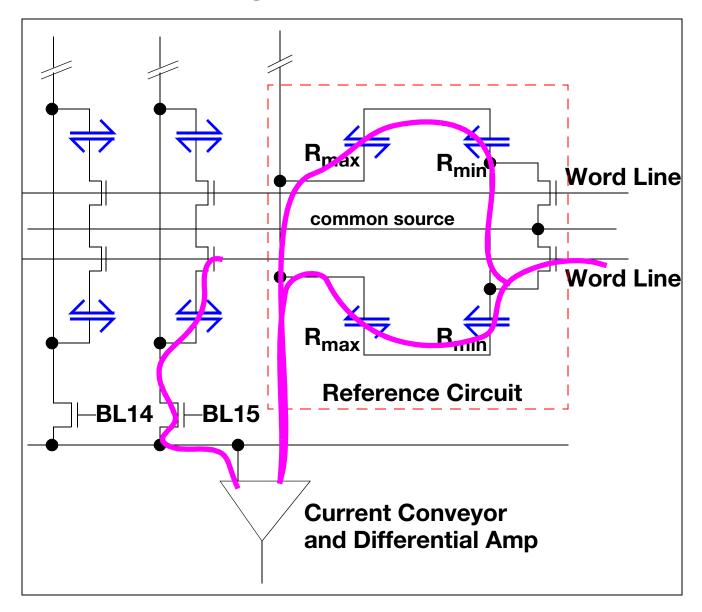

## **MRAM Reference Circuit**

**Reference Cell**

Reference Cell uses Parallel/Serial combination of MTJ's in two memory states to generate "mid resistance" reference between those two states

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 18

# UNIVERSITY OF MARYLAND

# **MRAM Segment**

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 19

# Motorola 1 MBit MRAM Chip

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 20

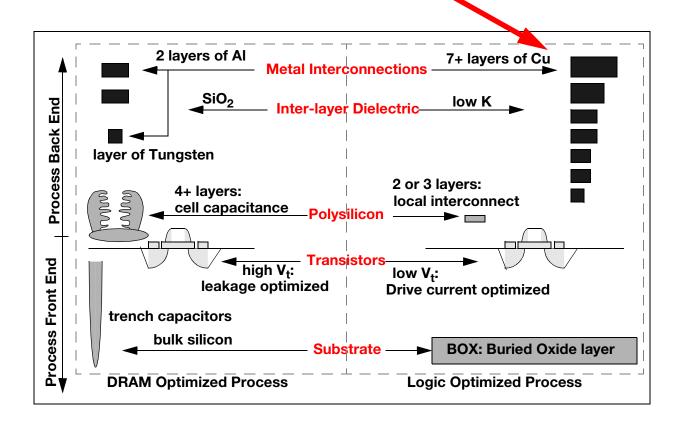

# **Process Compatibility**

Can be built between metal layers above active silicon

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 21

## **MRAM Summary**

- Non Volatile

- No need to refresh

- (potentially) High density

- Non destructive read

- High write current.

- Read speed = write speed; < 50ns</li>

- Unlimited R/W endurance

- Soft error immunity

- Material compatibility with CMOS logic and DRAM?

- Currently, large cells, but \*may\* scale down to DRAM/Flash levels of 6 F<sup>2</sup>.

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 22

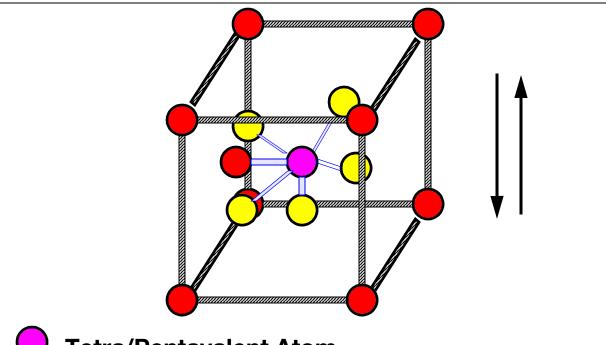

## **FeRAM Cell**

- Tetra/Pentavalent Atom

- Di/Monovalent Metal Atoms

- Oxygen Atoms

PZT (PbO, ZrO<sub>2</sub>, TiO<sub>2</sub>) Lead-Zirconate-Titanate unit cell

**Applied Electric Field Moves Center Atom**

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 23

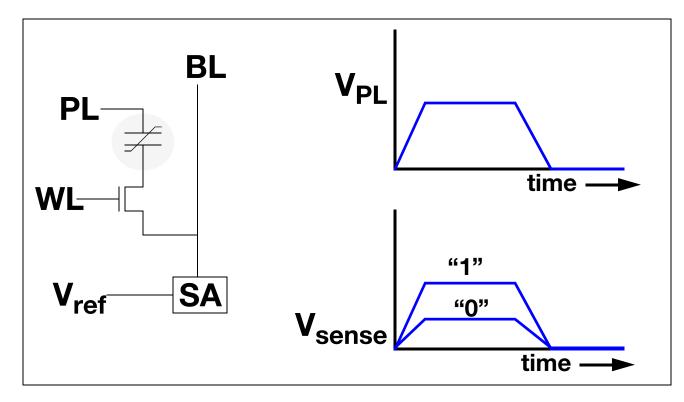

# **FeRAM Cell Operation**

- Ferroelectric material can be polarized into two stable states. States can be maintained without power

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 24

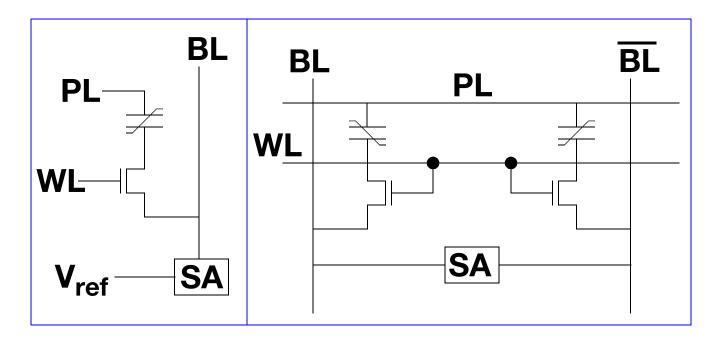

## **FeRAM Circuit Structure**

1T1C: DRAM-like 2T2C: Built-in reference

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 25

## **FeRAM Summary**

- Non-volatile (no refresh)

- Destructive read

- Low voltage and low power

- Fast read and fast write (compared to NVM)

- limited R/W endurance (< 10<sup>9</sup> reads)

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 26

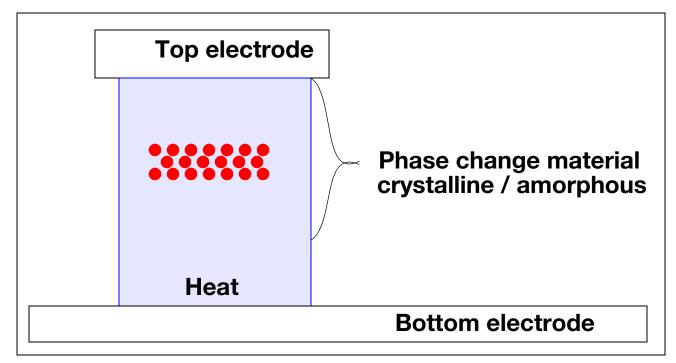

# **Phase Change Memory**

Heat, then . . .

Fast cool down = amorphous. High resist. Slow cool down = crystalline. Low resist.

Differences in resistance = "0" or "1"

Same material used in re-writeable CD/DVD optical disks (GeSbTe)

Spring 2014

CS-590.26 Lecture E

Bruce Jacob David Wang

University of Crete

SLIDE 27

## **PCRAM Summary**

- Rad Hard (SEU has limited/no effect)

- Non destructive read

- Direct write (no need for DRAM Sense Amp style Read-Modify-Write)

- Low voltage and low power

- Fast read and medium speed write (fast compared to NVM)

- Unlimited read cycles

- Limited write cycles ( < 10<sup>12</sup>); Large write current can overheat element, element can be stuck at low resistance state

- Can scale to 22nm tech (source: Intel)