#### **ABSTRACT**

Title of Thesis: ARCHITECTURAL SUPPORT FOR EMBEDDED

**OPERATING SYSTEMS**

Degree candidate: Brinda Ganesh

Degree and year: Master of Science, 2002

Thesis directed by: Professor Bruce L. Jacob

Department of Electrical and Computer Engineering

This thesis investigates hardware support for managing time, events, and process scheduling in embedded operating systems. An otherwise normal content-addressable memory that is tailored to handle the most basic functions of a typical RTOS, the CCAM (configurable content-addressable memory) turns what are usually O(n) tasks into O(1) tasks using the parallelism inherent in a hardware search implementation. The mechanism is modelled in the context of the MCORE embedded microarchitecture, several variations upon  $\mu$ C/OS-II, a popular open-source real-time operating system and Echidna, a commercial real-time operating system. The mechanism improves the real-time behavior of systems by reducing the overhead of the RTOS by 20% and in some cases reduces energy consumption 25%.

This latter feature is due to the reduced number of instructions fetched and executed, even though the energy cost of one CCAM access is much higher than the energy cost of a single instruction. The performance and energy benefits come with a modest price: an increase in die area of roughly 10%. The CCAM is orthogonal to the instruction set (it is accessed via memory-mapped I/O load/store instructions) and offers features used by most RTOSes.

# ARCHITECTURAL SUPPORT FOR EMBEDDED OPERATING SYSTEMS

by

### Brinda Ganesh

Thesis submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Master of Science 2002

# Advisory Committee:

Professor Bruce L. Jacob, Chair Professor Gang Qu Professor Shuvra Bhattacharyya ©Copyright by

Brinda Ganesh

2002

#### **ACKNOWLEDGEMENTS**

I would like to thank my advisor Dr Bruce Jacob for having given me this oppourtunity to work on this project and for all the time, help and encouragement that he has given me over the course of its development.

I would like to thank Dr Stewart who has given valuable input to the development of this idea.

I would also like to thank my colleagues at the university - Aamer, Paul, Zahran, Ankush, Tiebing, Lei, Dave, Vinodh, Anasua, Aneesh for everything from technical discussions, insight and suggestions to bicycle rides and cups of tea.

On a personal note I would like to thank my parents, my sister Rupa, my grandmother and Deepak who have believed in me always. I am very grateful to Himanshu for the invaluable advice he has given me over the past couple of years. Finally I would like to thank my housemates - Vijaya, Anu, Lakshmi, Sharmila who lived with me and accepted my indifferent cooking and mood swings when the going got tough.

# TABLE OF CONTENTS

|   | Ack   | nowledgementsv                                           |

|---|-------|----------------------------------------------------------|

|   | List  | of Tables ix                                             |

|   | List  | Of Figures                                               |

| 1 | Intro | oduction and Motivation                                  |

|   | 1.1   | Characteristics of Embedded Systems                      |

|   | 1.2   | Current Trends in Embedded Systems                       |

|   | 1.3   | Motivation                                               |

|   |       | 1.3.1 Support for Process, Time and Event Management. 10 |

|   | 1.4   | Overview                                                 |

|   |       |                                                          |

| 2 | Bacl  | kground: Real-Time Operating Systems                     |

|   | 2.1   | Real-Time Systems                                        |

|   |       | 2.1.1 Real-Time Terminology                              |

|   |       | 2.1.2 Classification of real-time systems 16             |

|   |       | 2.1.3 Real-time system requirements 17                   |

|   | 2.2   | Real-Time Operating Systems                              |

|   |      | 2.2.1   | Scheduling                                         |

|---|------|---------|----------------------------------------------------|

|   |      |         | 2.2.1.1 Terminology                                |

|   |      |         | 2.2.1.2 Types of Schedulers                        |

|   |      | 2.2.2   | Time Services                                      |

|   |      | 2.2.3   | Inter process Communication and Synchronization 37 |

|   | 2.3  | Relate  | d Work                                             |

|   |      |         |                                                    |

| 3 | CCA  | AM: Des | scription                                          |

|   | 3.1  | CCAN    | A Structure                                        |

|   | 3.2  | CCAN    | M Module Interface                                 |

|   | 3.3  | Implei  | mentation                                          |

|   |      | 3.3.1   | CCAM Energy Model 62                               |

|   |      | 3.3.2   | Die Area Cost                                      |

|   |      |         |                                                    |

| 4 | Exp  | eriment | s                                                  |

|   |      |         |                                                    |

| 5 | Resu | ılts    | 74                                                 |

|   | 5.1  | Overh   | ead74                                              |

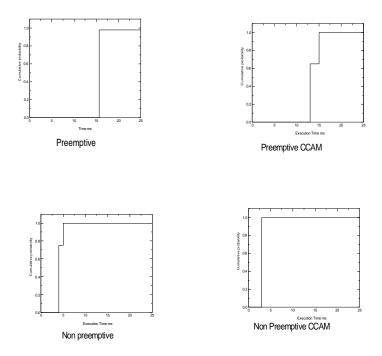

|   |      | 5.1.1   | Preemptive $\mu$ C/OS Configurations               |

|   |      | 5.1.2   | Non preemptive $\mu C/OS$ configurations 81        |

|   |      | 5.1.3   | Echidna                                            |

|   | 5.2  | Operating System Functional Measurements 90       |

|---|------|---------------------------------------------------|

|   | 5.3  | Jitter                                            |

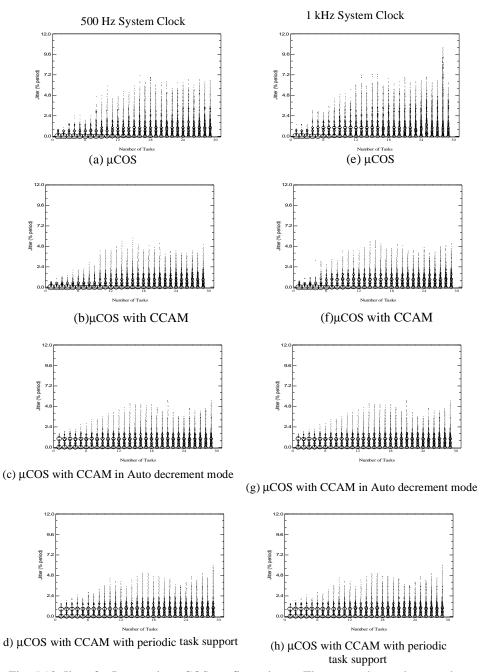

|   |      | 5.3.1 Preemptive μCOS Configurations 97           |

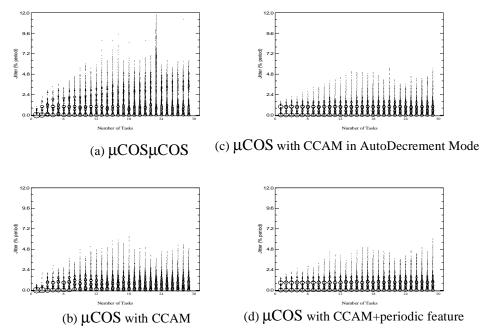

|   |      | 5.3.2 Non preemptive mC/OS Configurations 104     |

|   |      | 5.3.3 Echidna                                     |

|   | 5.4  | Response Time                                     |

|   |      | 5.4.1 Preemptive μCOS Configurations              |

|   |      | 5.4.2 Non preemptive $\mu$ COS Configurations 115 |

|   |      | 5.4.3 Echidna                                     |

|   |      |                                                   |

| 6 | Con  | elusion and Future Work                           |

|   | 6.1  | Conclusions                                       |

|   | 6.2  | Future Work                                       |

|   | Bibl | ography120                                        |

|   |      |                                                   |

# LIST OF TABLES

| CCAM Module Address Map          | , |

|----------------------------------|---|

| State Assignments for Run Status |   |

| CCAM Instructions                |   |

# LIST OF FIGURES

| Fig. 2.1. | Ready List in $\mu$ C/OS                                 |

|-----------|----------------------------------------------------------|

| Fig. 3.1. | CCAM Structure                                           |

| Fig. 3.2. | State Machine representation of Run Status of a Task. 44 |

| Fig. 3.3. | Instruction Layout of CCAM instructions51                |

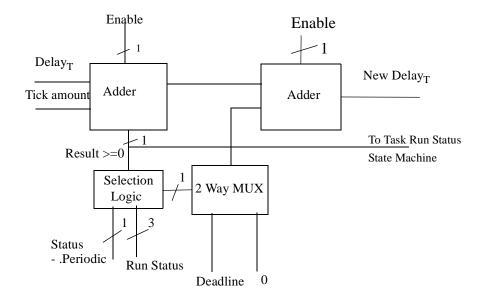

| Fig. 3.4. | CCAM Tick Module for handling Timeout Delays 55          |

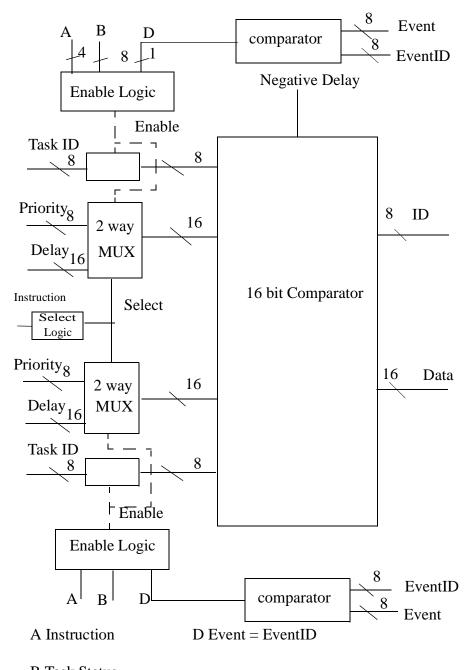

| Fig. 3.5. | Structure of Input Comparator Element                    |

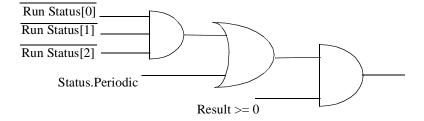

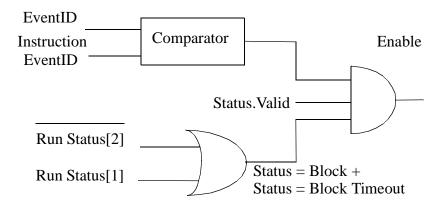

| Fig. 3.6. | Enable Logic for Priority /Delay Sort                    |

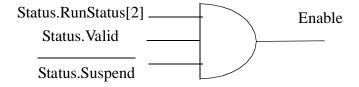

| Fig. 3.7. | Enable Signal for Release Event Priority Sort 61         |

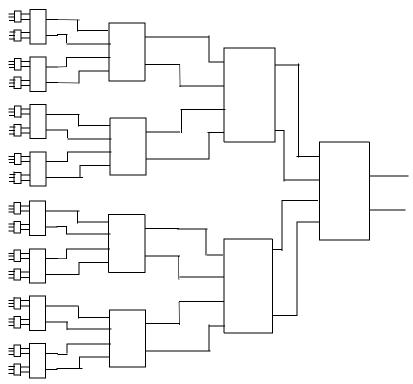

| Fig. 3.8. | Comparator Network                                       |

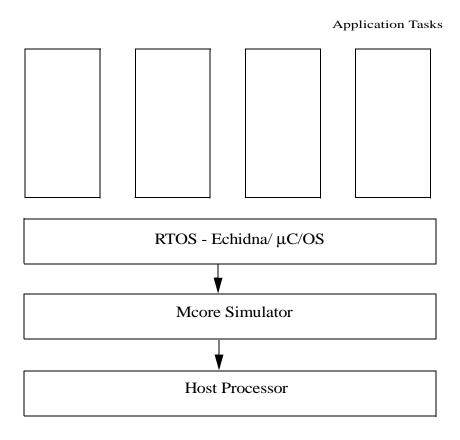

| Fig. 4.1. | Experimental Setup                                       |

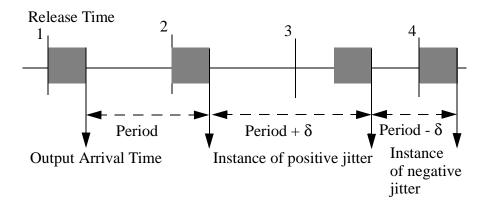

| Fig. 4.2. | Jitter Example70                                         |

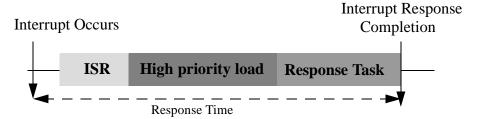

| Fig. 4.3. | Response Time to External Interrupt71                    |

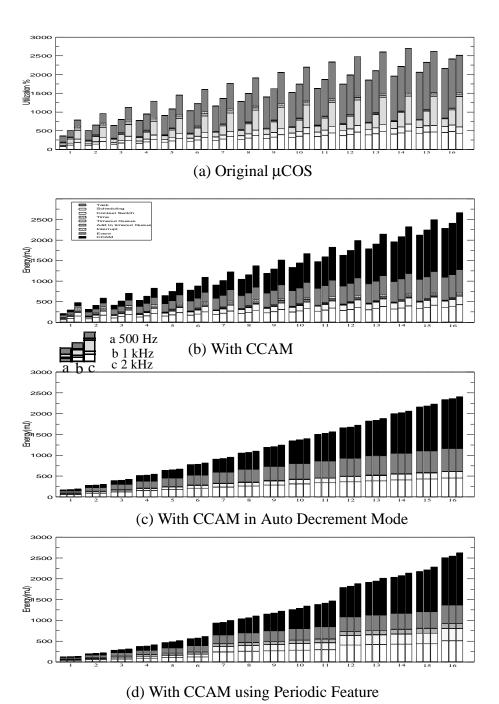

| Fig. 5.1. | Energy Consumption for preemptive μCOS configuration     |

|           | 75                                                       |

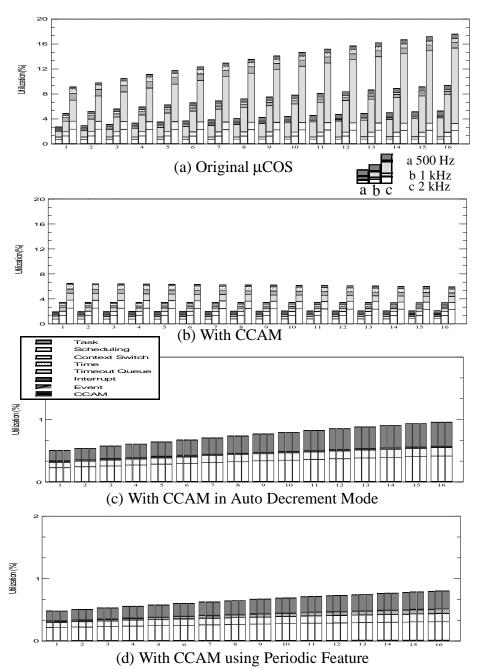

| Fig. 5.2. | Utilization for preemptive $\mu COS$ configurations 79   |

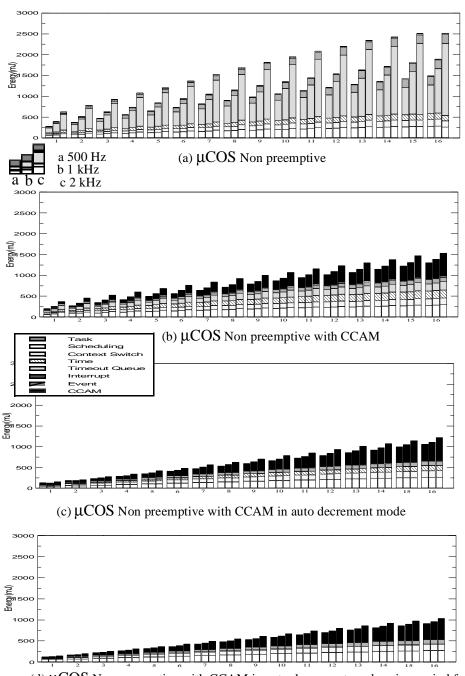

| Fig. 5.3. | Energy consumption of non preemptive $\mu COS$           |

|           | configurations83                                         |

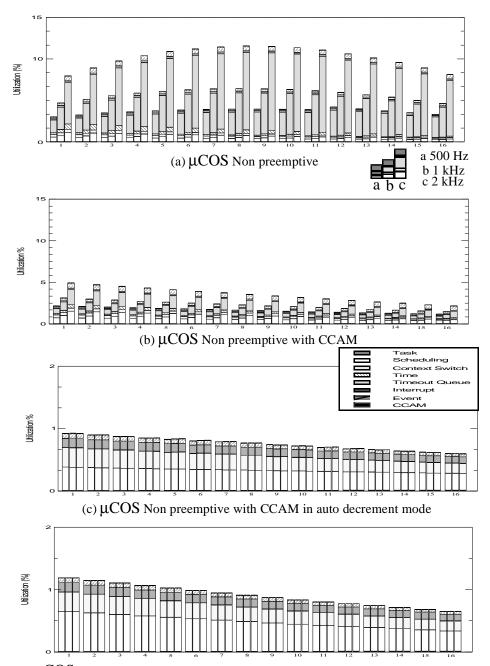

| Fig. 5.4.  | Utilization Overhead for non preemptive μCOS                 |

|------------|--------------------------------------------------------------|

|            | configurations85                                             |

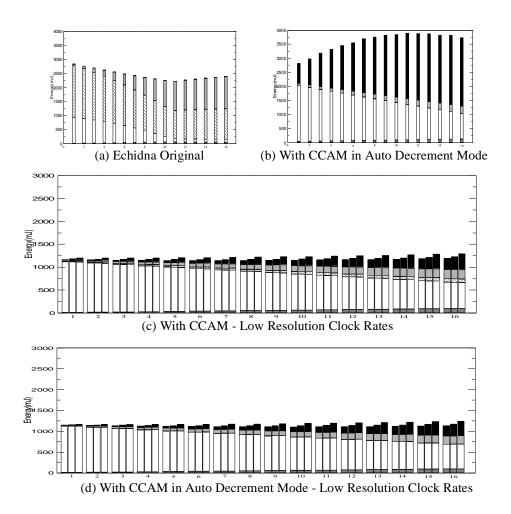

| Fig. 5.5.  | Energy Consumption of Echidna based configurations88         |

| Fig. 5.6.  | Operation System Overhead for Semaphore Pend 91              |

| Fig. 5.7.  | Operation System Overhead for Semaphore Post 92              |

| Fig. 5.8.  | Operation System Overhead for Time Delay93                   |

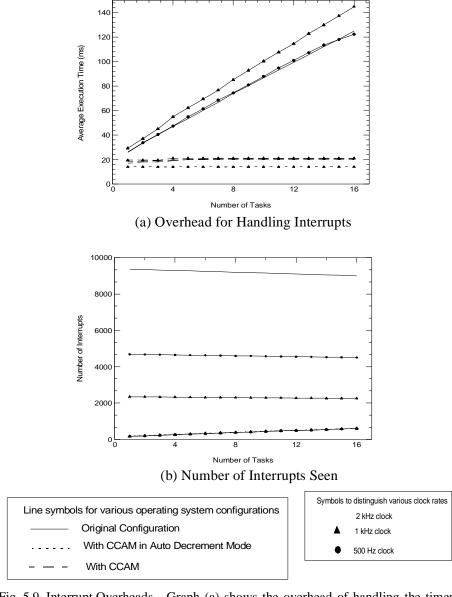

| Fig. 5.9.  | Interrupt Overheads                                          |

| Fig. 5.10. | Jitter for Preemptive $\mu COS$ configurations               |

| Fig. 5.11. | Jitter for Preemptive $\mu COS$ configurations with a system |

|            | clock rate of 2 kHz103                                       |

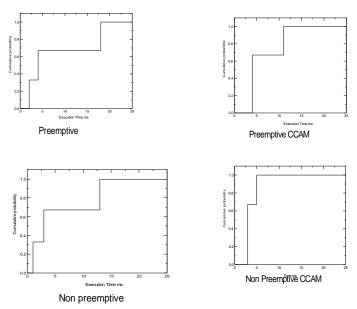

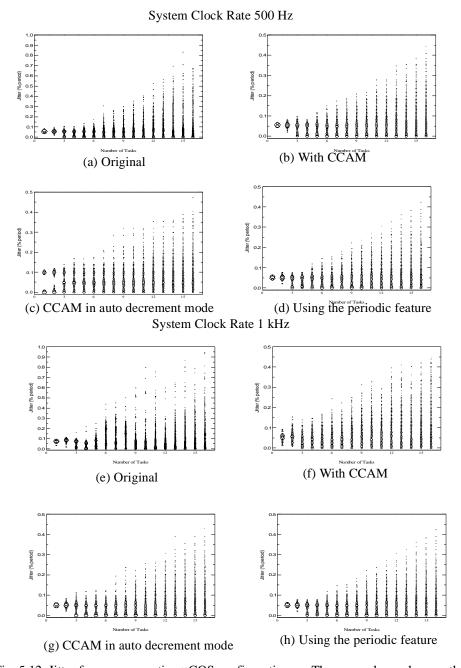

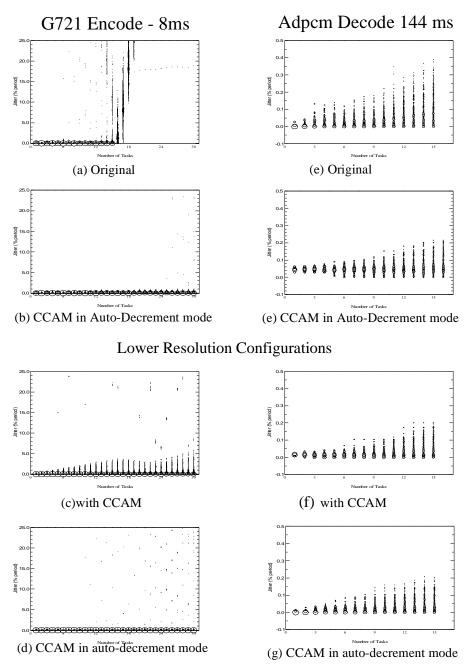

| Fig. 5.12. | Jitter for nonpreemptive μCOS configurations 106             |

| Fig. 5.13. | Jitter for Echidna based configurations 109                  |

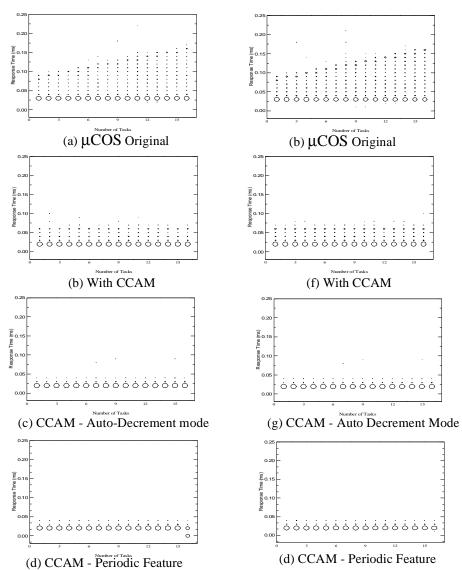

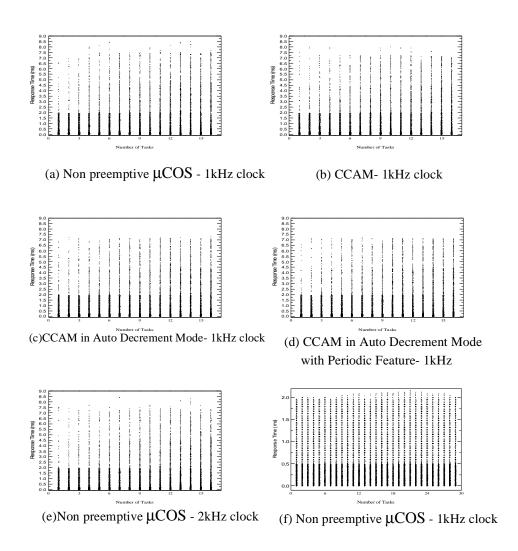

| Fig. 5.14. | Interrupt Response Time for Preemptive $\mu COS$             |

|            | configurations112                                            |

| Fig. 5.15. | Response Time to Aperiodic Interrupts for Non preemptive     |

|            | μCOS configurations113                                       |

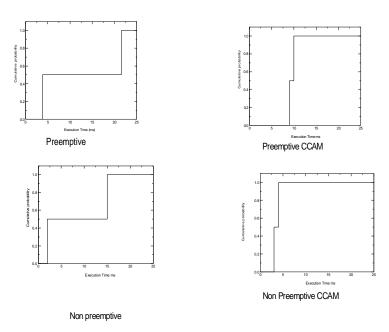

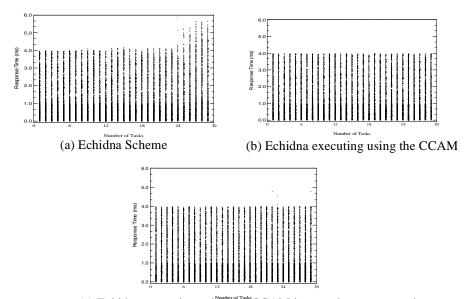

| Fig. 5.16. | Response Time to Interrupt for Echidna based                 |

|            | configurations116                                            |

#### CHAPTER 1

#### INTRODUCTION AND MOTIVATION

The modern world is characterized by the integration of computing power into our lifestyles. The incorporation of "intelligence" into every device and gadget forms the basis of the ongoing computing revolution. This new wave is characterized by freeing computing power from a traditional desktop environment and making it an all pervasive yet invisible force. It is this demand for "hidden computing power" which has fuelled the growth of the embedded systems marketplace. Current estimates indicate that there are more than 5 billion embedded processors being used in the world[1] and that this number is constantly growing with nearly 4 billion dollars worth of micro controllers being sold annually.

## 1.1 Characteristics of Embedded Systems

Embedded System design factors in various issues which are not considered in the design of high performance desktop systems. These include:

Low Cost: A large number of embedded products including cell phones, electric shavers, toasters etc. are in markets where the end user is unwilling to spend a little extra for slightly better performance or a few extra features. Embedded designers are thus forced to design systems with optimal price/performance ratios and extract the required performance at the least cost. The result of this is that the resources available to the designer are minimal. For example an embedded system rarely has more than a few MB of memory available.

Low Power: Power consumption is another critical factor in the design of these systems. This is largely because most of these systems are battery operated and are expected to remain active for long periods of time. e.g. pacemakers, sensors, cell phones, PDAs. They are often deployed in harsh uncontrolled environments.eg digital sensors. The size of these systems is often a deterrent to incorporating the cooling systems required. Thus low power is an essential feature.

**Predictability:** Owing to the large number of real-time applications that most embedded systems run it is of paramount importance that they exhibit predictable behavior. This implies that under all possible events and conditions one can predict the behavior of the system. In these systems the underlying hardware has to guarantee that any code

running on it will have the same execution overhead every time it is run. The software is usually designed for the worst case scenario and such that the overheads are deterministic.

**Responsiveness:** Embedded applications, like control system applications, are event driven and need to respond quickly to these events. Such systems rely heavily on interrupts and have to designed to have low interrupt response times as well as low interrupt processing overheads.[9]

**Temporal Accuracy:** Distributed embedded applications which manage remote databases and network devices all require highly precise time granularities [8]. The resolution and accuracy is expected to be in the order of microseconds for most of these applications.

#### 1.2 Current Trends in Embedded Systems

The absence of general features and extremely tight design constraints has led to most embedded applications being extremely specialized and highly optimized. A typical embedded design procedure goes through several steps [3],[10]

- Design Specification

- Hardware/ Software Partitioning

- Parallel HW/SW development

- System Integration and Testing

Each of these steps relies heavily on the experience of the designer. The actual development involves several pain staking steps including writing hand-coded assembly, developing your own specific job scheduler, resource manager and device drivers, addressing code placement and memory space issues and customizing hardware modules for particular design specifications. [3]

All these factors have lead to little scope for errors in the design space. The inflexibility of the design makes the overhead of correcting errors in the design or accounting for modifications in the specifications very high. Additionally it allows for very little reusability of the design or portability. New versions of the product may require complete redesign or in some cases considerable rework for incorporating additional functionality. Further, studies show that more than fifteen percent of developers report that between 26 and 50 percent of their projects are never finished. Forty-one percent report that up to 25 percent of their projects are abandoned. [4]

With more and more players in the embedded devices market a reduced time-to-market is one of the chief concerns. In order to achieve faster timeto-market and prevent abandonment of projects embedded developers are moving towards designing systems which are more generic and flexible.

Designers now chose more generic hardware, program in higher level languages and use third party tools for their development.

So what then does the market offer to an embedded system developer? In terms of hardware it is a set of processors which are reminiscent of the desktops of a bygone era. e.g. 68000 and Z80 designs [17, 16] or strippeddown versions of contemporary high-performance desktop processors, e.g. MIPS, PowerPC and x86 designs. [12,14,15]. By definition, these designs are born of high-performance design goals, not embedded-systems design goals. Similarly, many hardware structures such as caches and memorymanagement units that appear in embedded processors—even in those processors that are designed specifically for the embedded market—are based on high-performance designs, for example the MMUs and caches in the ARM and Hitachi SH7750 architectures [11,13]. Some of the embedded microprocessors have incorporated embedded design requirements like low power and reduced die area. e.g. the StrongARM, and Motorolas's Mcore. Several processor vendors have also come up with strategies to improve code density. These strategies are based on compressing 32 bit instructions to 16 bit opcodes and decompressing it on the fly e.g. ARM Thumb extension, using variable length instruction length e.g. Infineon Camel [18] or using fixed 16-bit instructions e.g. Hitachi Super H architecture.

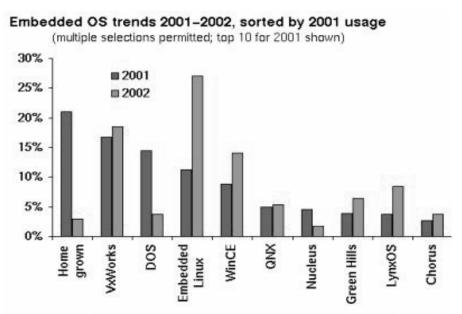

Source: Evans Data Corporation 2001 Embedded Systems Developer Survey

Embedded software developers also have a growing number of third party tools at their disposal. These tools help embedded engineers to work at higher levels of abstractions on designs and specifications, reduce the number of design errors and reduce development time by allowing reusability. They include:

- Design automation tools for system-on-chip designs and hardware software co-design e.g. Synopsys' System Studio, ARM® Integrator/CP (TM) development platform

- · software modelling tools e.g. Artisan,

- integrated development environments e.g. Code Warrior, Multi 2000,.

#### • Operating Systems e.g. vxWorks, embedded Linux

Their growing popularity is reflected by several strong market indicators. The EDA embedded design market was a 1.5 billion dollar market in the year 2000. Also a recent study about operating system usage in the embedded industry indicates that "home grown" operating systems are soon to be a thing of the past. The percentage of developers using their own operating system is expected to drop by nearly 80% from 25% in the year 2001 to 5% the following year. This rapid downturn in the roll your own category is the direct consequence of the growing complexity of embedded applications and the unwillingness of companies to invest precious man hours on reinventing the wheel, i.e. developing their own operating system services when they can get it from a reliable third party.

#### 1.3 Motivation

Because of the architecture-level focus on high performance computing, many of the microarchitecture structures in use today—even those used in architectures aimed specifically at embedded systems—are geared toward the goals of high-performance computing, not embedded computing. As a result, there is very little architectural support in today's embedded processors for predictable performance or high resolution timing.

In addition to the previously mentioned legacy mechanisms at the architecture level that frustrate the design of embedded systems (mechanisms such as branch prediction, data prediction, hardware-managed caches, outof-order issue, etc.), there are numerous legacy mechanisms at the systemsoftware level that cause similar problems. For instance, the time management scheme found in most operating systems uses a periodic clock interrupt to increment an internal counter and thereby update the operating system's internal notion of time in the external world. This scheme is simple and effective and is generally used to handle clock resolutions on the order of ten milliseconds; the scheme does not scale particularly well beyond that, though interpolation schemes exist to increase the resolution further, as discussed later. Nonetheless, to achieve resolutions down to microsecond accuracy is non-trivial using conventional means, and yet these are exactly the types of resolutions necessary for high-performance embedded systems [19,20].

Real-time literature is rich with innovative scheduling schemes targeted towards achieving the timing requirements of the workload in an optimal fashion.[21,22] A larger number of these schemes including EDF are rarely implemented in commercial real time operating systems owing to the substantial and variable software overhead.

Our solution to the problem is to support embedded systems by looking at architectural mechanisms and combined hardware/software schemes that address the goals of embedded systems. In particular, we present an investigation of the following instances of hardware support for embedded operating systems:

special CAM-based hardware  $^1$  to help turn scheduling tasks that typically run in O(n) time into tasks that run in O(1) time; and

a medium-resolution internal clock (500 µsec.) that provides both good accuracy and low overhead, especially if coupled with the CAM hardware.

We find that, by using these mechanisms, one can achieve better timing accuracy and more predictable performance without requiring more CPU overhead or energy. In fact, the scheme simultaneously reduces both CPU overhead and energy consumption. Our experimental set-up is a highly accurate software model of the Motorola MCORE processor [14]; our simulator runs the same unmodified application and operating system binaries as our test hardware and models energy consumption of the CPU as well [2]. The embedded operating system under study is  $\mu$ C/OS-II, a popular public-domain, open-source RTOS [23]. In our benchmark tests of the CCAM hardware, we saw the maximum jitter in the system decrease, we

<sup>&</sup>quot;CAM" stands for content-addressable memory, another term for fully associative cache. The hardware data structure is used to search a small set of objects in parallel for a matching value or least/greatest value; it essentially behaves like a small, fast hardware database.

were able to increase the number of tasks in the system by a factor of two beyond that achievable by software means alone, and on an average we saw a factor-of-two reduction in energy consumed.

The gains come at a price, though detailed discussion lies beyond the scope of this paper. The cost is an increase in die size that is significant when compared to the processor core alone but less so when compared to the size of a typical embedded chip that includes RAM, ROM, and various peripheral devices. The CAM structure and associated timing hardware account for roughly 2000 register-bit equivalents (RBEs, a process-independent unit of die-area measurement [27]) for a 64-task CAM. Given that a 32x32 register file requires roughly 1000 RBEs, this can double the size of a small cacheless embedded core such as MCORE. However, once peripherals and memory structures are added, the overhead is less dramatic; the 64-task CAM structures represent more moderate 5% increases in the size of a typical embedded processor, such as the MCORE-based MCM2001 [15], that includes external RAM, ROM, and peripheral I/O devices.

#### 1.3.1 Support for Process, Time and Event Management

There are numerous facilities one could investigate to help the performance of embedded systems. We chose to attack the facility that is com-

mon to all embedded operating systems and represents a variable overhead in each one (i.e. its overhead scales with the number of tasks or processes in the system). This facility is the management of processes and events, or scheduling.

The design of the mechanism that we investigate is based on the needs of the operating system, which must perform the following functions:

determine, from a set of tasks, which has the highest priority or nearest deadline;

determine which in a set of tasks need to be updated when a semaphore or lock is released;

provide to tasks a mechanism to suspend themselves for a specified period of time or until a specified event occurs.

Scheduling is intrinsically an O(log n) or O(n) operation, as it involves ordering and searching a set of n tasks, based on priority, earliest deadline, etc. Scheduling represents an overhead that is variable, depending on the size of the task set, and is thus a good target for optimization. The scheduling process as implemented in most embedded operating systems is actually O(n) because the task sets are typically small (rarely more than a few dozen tasks) and maintained in short lists or arrays—not binary trees. The constants involved in maintaining a balanced binary tree would tend to

make the  $O(\log n)$  implementation actually take more time than the simpler O(n) linked-list implementation.

We note that the embedded operating system's requirements (e.g. search a small set of items for a matching value or a greatest/least value) map extremely well to a CAM structure. By implementing these functions in hardware, one can take advantage of hardware's ability to perform multiple comparisons in parallel and so turn this O(n) operation into an O(1) operation; i.e. the procedure takes the same amount of time no matter how large the task set, up to the size of the CAM structure.

#### 1.4 Overview

This report is based on the following lines. Chapter 2 will provide a background on the working of real-time operating functions. Chapter 3 will be an overview of the CCAM- a description of its interface, its operation and design. Chapter 4 will describe the experimental setup while in Chapter 5 the results of the experiments will be presented. Chapter 6 will provide a summary of the work and give an insight into future work.

#### **CHAPTER 2**

#### BACKGROUND: REAL-TIME OPERATING SYSTEMS

#### 2.1 Real-Time Systems

Donald Gilles' definition of a real-time system[28] is as follows:

"A real-time system is one in which the correctness of the computations not only depends upon the logical correctness of the computation but also upon the time at which the result is produced. If the timing constraints of the system are not met, system failure is said to have occurred."

This implies not just that real-time systems have to respond to external stimuli or service tasks within a specified timberland but that, irrespective of the system load, this action has to be predictable. Additionally it is also desirable that real-time systems achieve their functional correctness and timeliness while being highly utilized.

A good example of a real-time system is robot arm working on a conveyor belt. The robot arm has to pick a certain part off the belt. In this case the robot arm will not be able to pick up the part if it attempts to do so either late or early. Another more complex example is an air traffic controllers. These systems are required to monitor the movement of aircraft and changes in the weather conditions in their coverage area and based on this

13

information they have to be able to calculate the trajectory of aircraft in the system, schedule its landing and provide all this information to a human controller. These systems have to perform a wide variety tasks including data and image processing, updating data bases and intensive compution. Each of these tasks have different response times e.g. weather updates may take place every 2 seconds while display refreshes have to occur every tenth of a second. Additionally the system has a variety of workloads some of which are periodic, like weather updates or display refreshes and others which are aperiodic e.g. aircraft entry into airspace. The system response to each of these tasks has a well defined upper bound which has to be achieved irrespective of the system load i.e. changing weather conditions or number of aircraft.

#### 2.1.1 Real-Time Terminology

There are several terms which are commonly used in discussion of realtime systems. This section is an overview of some of these terms.

**Job :** This refers to a unit of work which can be scheduled or executed by the system. For example a function which reads the input off a memory port can be considered a job.

**Task:** This is a collection of related jobs which collectively achieve a single function. For example a collection of jobs which read data from

a memory location, perform certain computations and write the result to another location can all be considered to constitute a task. A task is said to be periodic if it has to be run at regular intervals. An aperiodic or sporadic task is run when a certain infrequent event occurs.

Release Time: This is the earliest time at which a task becomes available for execution. A job can be executed any time at or after its release time. If all the jobs in a system are available for execution right at the outset than it is assumed that no job has a release time. For example a periodic job may be released every 100 ms for execution. The release times for this job is 100 ms, 200 ms, 300 ms and so on and so forth.

**Deadline:** This refers to the instant of time within which the job has to complete execution. If the periodic job mentioned above has to complete prior to the release of the next job than its deadlines are 200 ms, 300 ms, 400 ms etc.

**Response Time:** This refers to the time interval between the release time of a task and its completion time i.e. the instant it completes execution. For example if a job is released at 10 ms and completes execution at 25 ms, than the response time is 15 ms.

**Tardiness:** This refers to how late a task completes with respect to its deadline. A task is said to have a tardiness of zero if it completes at or before its deadline while a task which completes after its deadline has a tardiness equal to the difference between its completion time and its deadline.

#### 2.1.2 Classification of real-time systems

Real-time systems are classified based on the strictness of their timing requirements or the criticality of their deadlines. There are two categories

Hard Real-Time Systems: A real-time system is said to be a hard real-time system when it has extremely tight timing constraints and strict deadlines. These systems execute critical tasks whose delayed execution or non execution would have catastrophic consequences.

Hard real-time tasks are expected to have a tardiness of zero and exhibit deterministic temporal behaviour. This implies that they are expected to complete at or before their deadlines and that their execution is absolutely guaranteed. Typical hard real-time applications include antilock braking systems, pace makers and air flight controllers.

**Soft Real-Time Systems:** On the other hand soft real-time systems are more concerned with best-effort services. [6,7] These systems execute less critical tasks and can tolerate missed deadlines. Unlike in a hard

real-time system where results from late tasks have no usefulness, tasks in a soft real-time system continue to be useful even if late. The usefulness of their results gradually tapers off with the tardiness of the task rather than dropping abruptly to zero at the instant after the deadline. In general the performance of these systems is described in probabilistic terms i.e. 95% of the time the data arrives on-time.

Typical examples include multimedia applications like MPEG decoders and encoder, telecommunications applications like internet telephony and some sorts of data acquisition applications.

## 2.1.3 Real-time system requirements

A real-time system has several requirements to fulfill including:[28, 25]:

**Timeliness:** There is a certain upper bound within which the system is expected to finish certain tasks. The time within which the task has to be completed is termed the deadline. The criticality of the deadline depends on the function of the system.

Simultaneity or simultaneous processing: The system should be able to process events that occur simultaneously and still meet all deadlines. This implies that a real-time system should be inherently parallel in nature. This can be achieved by making the system either a multiprocessor system or by using a multi-tasking model. A distributed real-

time system or a heavily interrupt driven system are cases where simultaneous events occur on a regular basis.

**Predictability:** One common goal in real-time system design is predictability. Predictability implies that it can be demonstrated that the system fulfills its requirements under a variety of situations. This implies that predictability is subject to the assumptions made while determining it[29].

Predictability of simple static real-time systems is much easier to determine and design for. This is because the number of tasks in these systems are known and their worst case execution times are available up front. In addition the system consist of largely either hard real-time or soft real-time applications. The predictability of these systems then can be expressed using a single number depending on which component i.e. interrupt latency or fixed periodic task behavior, is the dominant factor.

Predictability of a complex real-time system on the other hand is more difficult to design for. This is because these system have a variety of tasks with different levels of criticality. The environment in which these systems function is also non-deterministic in nature. In general predictability for these systems can be viewed to have two components.

The first which is a more macroscopic is concerned with overall system performance. This component requires demonstration that critical tasks performance is 100% guaranteed and that non-critical tasks achieve a performance which is close to the maximum actual performance. The other is with respect to individual tasks or task groups in the system. The second more microscopic look at the system considers the specific periodicity timing and deadline requirements of the individual tasks.

**Dependability:** As real-time systems are often deployed on extremely critical missions, they have to be dependable. Dependability is defined as "the trustworthiness of a computing system which allows reliance to be justifiably placed on the service it delivers." [30]. A dependable system has the following attributes

- Availability This is the extent to which a system is ready for use

- Reliability This is a measure of the extent to which the system's actions and results can be trusted.

- Safety This is the extent to which the system does not harm the surrounding environment itself.

- Security This is the extent to which the system is safe from unauthorized access or tampering.

A dependable system has to provide for the following [5]

- Fault Prevention: Prevention of fault occurrence,

- Fault Tolerance: Correct functioning in the event of faults

- Fault Removal: Elimination of current faults

- Fault Prevention: Forecast future faults and prepare for their prevention or effective handling.

To make a real-time system dependable it would require providing for exception handling, incorporating fault tolerant features into the scheduler and designing for correct functioning in the event of partial hardware failure.

#### 2.2 Real-Time Operating Systems

The Posix Standard 1003.1 defines real-time in operating systems as:

"Real-time in operating systems: the ability of the operating system to

provide a required level of service in a bounded response time."

This implies that a real-time operating system aka the RTOS is expected to provide basic operating system functionality like scheduling, timer services, synchronization primitives, inter-process communication mechanisms among other things in a deterministic fashion. This implies that the overhead of the operating system should be consistent for all invocations.

RTOSes are expected to have a small size as they are used on systems with scarce memory resources. Typical RTOS memory footprints are on the order of several 100 kilobytes. As the subset of operating system services used is heavily application dependent these systems have to be modular, scalable and completely configurable. Besides the basic real-time kernel services commercial RTOSes offer a variety of optional services including support for networking, file system I/O, multiprocessor systems, graphics etc. The extent of the extensibility of modern day RTOS' can be gauged by looking at the flexibility offered by the commercial RTOS, vxWorks. vxWorks offers nearly 100 different options to the real-time programmer which can be used to generate a variety of configurations. [25]

In this chapter we examine some of the basic real-time kernel services, design choices and implementations.

#### 2.2.1 Scheduling

Scheduling is the mechanism which determines which job has to be executed from the pool of jobs in the system. The logistics behind the decision making mechanism is based on the scheduling algorithm implemented.

#### 2.2.1.1Terminology

Typical scheduling algorithms used in RTOSes are termed correct because they generate valid schedules

Valid Schedule: Jane Liu [25] says that a valid schedule has to guarantee that all tasks are scheduled only after or when they are released and such that all resource and precedence constraints are met.

**Feasible Schedule:** A valid schedule in which every task meets its deadlines.

**Optimal Scheduler:** A scheduler which always generates a feasible schedule if the given set of jobs can have one.

Preemption: This refers to the ability of the scheduler to halt execution of a task in favour of another task with higher priority or criticality.

Permitting preemption allows the scheduler to service sporadic tasks and higher priority tasks which are released during the execution of the current task. A system where a task can continue executing without being ever switched out is a nonpreemptive one.

**Schedulable Utilization:** This represents the upper bound of the utilization of the periodic tasks in the system for which a particular algorithm can generate a feasible schedule. Clearly the higher the schedulable utilization the better the algorithm is.

**Ready Queue:** It is the set of all tasks in the system which have been released are available for execution.

Pause Queue /Timeout Queue/ Delay Queue: It is the set of tasks which are not available to run till the passage of certain time i.e. the delay of the task

## 2.2.1.2Types of Schedulers

Scheduling is one of the most heavily researched areas in the real-time world. The result is a plethora of schedulers which tackle a wide range of application types and offer varying services and utilizations. The three most commonly used approaches to scheduling are

**Clock-driven:** This is an off-line scheduling mechanism common in systems where the nature of the workload i.e. execution times, relative deadlines etc. are known exactly at the point of system design. Jobs in systems employing a clock-driven scheduler are executed in a predetermined manner. The run time overhead of scheduling in these systems is negligible.

Weighted round robin: This is the commonly used approach in systems with time-shared applications. Tasks which are ready to run are placed in a FIFO queue. Starting from the head of the queue each task is executed in turn for a single time-slice. If the job does not complete at the end of its time slice it is preempted and placed at the end of the queue.

This technique is used in networking applications where messages have to be sent or received from several ports. The advantage of this scheme is that the overhead of inserting a task on the queue or removing it off the queue is constant. The downside is that the response time of a task is proportionate to both number of tasks in the queue and the number of time slices it takes to complete.

**Priority driven approaches:** Schedulers of this type base their scheduing decision based on some sort of priority. In these systems each task is associated with a priority. This priority is based on either off-line computations or on-line run-time calculations. Priority schedulers always schedule the task with the highest priority.

Thus there are two types of priority driven schedulers

**Fixed or Static Priority Schedulers:** The priority of tasks in these systems is fixed at the outset using standard off-line methods like Rate-Monotonic Analysis [21] and Deadline -monotonic analysis. RMA assigns tasks priorities based on their periods. The shorter the period, the higher the priority of the task. These priorities are fixed for the lifetime of the system.

The characteristics of a fixed-priority scheduler are:

- Good predictability: Systems using a fixed priority scheduler can be

validated easily using static off-line methods. Additionally in an

overloaded system or in the event of job over runs one can easily predict

that higher priority jobs will be serviced and the lower priority jobs will

miss their deadlines.

- Schedulable Utilization: It can be mathematically proven that the

schedulable utilization of a fixed-priority scheduler is not very high. The

schedulable utilization of RMA degrades exponentially from the best

case of 82% for a system with two tasks to nearly 69% to a system with

10 or more tasks.

- Simplicity: As tasks are associated with the same priority level through out their life this makes for easier system design, implementation and validation.

Fixed priority schedulers are the common choice in most standard real-time systems. Real-time systems support anywhere from 64 different priority levels to 256 different priority levels. Some operating systems allow multiple tasks to share the same priority level while others allow only one task to be at a certain priority level.

In order to support fixed priority scheduling in a system with unique priority levels one of the approaches is to maintain a ready queue which is sorted based on priority. Selecting the next task to run involves just looking at the first element in the queue and hence has a constant low overhead. Inserting tasks onto the list has a variable overhead and is dependent on the number of priority levels and tasks in the system. Another approach would be to maintain an unsorted ready queue. Every scheduling instance the scheduler traverses the entire queue and determines which task to run in the next interval. This mechanism is common in general-purpose operating systems like Linux where the operating system traverses the entire queue, calculates the current goodness of the task and uses this value when it makes it selection. The scheduling operation in this case has a constant overhead. But this determinism is achieved at very high costs.

All the mechanisms described above have overheads which scale with the number of priority levels. This is not desirable in an embedded system where it is desired that the RTOS overhead is not just low but also does deterministic and ideally independent on the workload i.e. its nature, size etc.

One of the methods used to reduce the overhead and still achieve determinism is to employ bit vectors. This mechanism is employed in  $\mu$ C/OS.

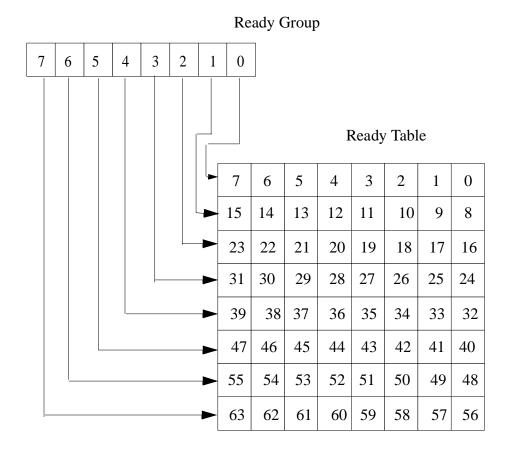

Fig. 2.1. Ready List in  $\mu$ C/OS. The figure shows the ready list in  $\mu$ C/OS which is divided into a two level data structure consisting of a ready group and the ready table. Individual tasks have an entry in the ready table and a group of tasks have a single bit entry in the ready group.

This is achieved by first partitioning the tasks into groups. This grouping is based on the priority levels of the individual tasks. The ready list of  $\mu$ C/OS is shown in Figure 2.1. For e.g.  $\mu$ C/OS has 64 tasks which are partitioned into 8 unique groups where tasks in group 1 will have a higher priority than those in group 2 but a lower priority than those in group 0. Each group is associated with a bit vector which is set when any task in the group is ready

to run. In  $\mu$ C/OS a single byte can be used to hold the group bit vectors. Each group in turn is associated with a byte of bit vectors which are associated with individual group members. Entering a task on the ready list or the two level bit vector structure involves setting the bit associated with the task's group and the bit associated with the task in its groups bit vector table. Scheduling in  $\mu$ C/OS essentially involves using this two variable ready list to determine which task to run. It does this by performing a 2 step inverse lookup operation. Thus the overhead of inserting or removing a task from the ready list or selecting the next task to run is constant. But the trade-off is the increased kernel size required for maintaining an inverse lookup table of 256 entries. This particular implementation of the selection procedure is not very scalable as the size of the inverse lookup table increases exponentially with the number of priority levels in the system.

Alternate implementations with bit vectors do away with the bulky inverse lookup table. This is done by associating a unique bit vector to every priority level in the system and performing a number of comparisons in order to determine the highest priority level job available. The number of such comparisons depends on the number of priority levels in the system, the size of the data in the system and the actual profile of tasks which are available at a given instant. Though there is a factor of variability in sched-

uling the worst and best execution times are not so vastly different to be an issue as in the earlier cases.

**Dynamic Priority Scheduler:** These schedulers assign different priorities to different jobs in a task. The priority of a task varies dynamically with respect to the other tasks in the system. Some dynamic priority schedulers include Earliest Deadline First - EDF and Least Slack Time First - LST.

EDF assigns priorities to jobs based on their absolute deadlines. Once a job is placed on the ready queue its order with respect to the other tasks on the queue is fixed. Thus the priority of a task can vary with each run making it a dynamic scheduler.

Some characteristics of EDF schedulers are

- Schedulable Utilization The EDF algorithm has a 100% schedulable utilization. This makes it an optimal algorithm for all loads.

- Predictability The disadvantage of this algorithm is that it produces

unpredictable schedules in overloaded scenarios. Late jobs which have

missed their deadlines have higher priority than later jobs which have

not missed their deadlines in turn to be late. This implies that

mechanisms to handle system overload and job overruns have to be

implemented.

Validation This system cannot be validated due its unpredicatability using known off-line methods. It requires dynamic validation which may not be feasible.

Echidna, a commercial RTOS, implements a non preemptive version of the EDF algorithm. The ready queue in Echidna comprises of tasks which are sorted on the basis of their deadline. The task at the top of the queue has the earliest deadline and hence the highest priority. Selecting a task to run has a constant overhead but inserting a task onto the queue is an O(n) operation. For preemptive system the overhead of placing tasks on the queue would be very significant.

An alternate way to implement this would be to maintain FIFO queues of threads with the same relative deadline [25]. The tasks in each queue are ordered on the basis of their absolute deadlines. Thus task selection involves just searching the heads of each of these queues. The overhead of this operation is dependent on the number of relative deadlines in the system. The complexity can be decreased from O(n) to O(log n) by using a priority queue for the first task of each FIFO queue. Inserting a task would involves adding the task at the end of the queue associated with its relative deadline. The complexity of this operation is 1 when the FIFO queue is non-empty and is O(n) when the queue is empty,[DIAGRAM]

As can be seen EDF schedulers are not easily implemented in software with low overheads due to their very dynamic property. This and their unpredictable behavior have not made them popular choices in the real-time operating system world.

#### 2.2.2 Time Services

The concept of time is central to a real-time operating system. Both task level and system level decisions are made on the basis of time. Time management can be said to have two aspects. The first aspect is concerned with the actual representation of the current time, its update and retrieval while the second aspect is concerned with the usage of this 'time' itself or its passage to make scheduling decisions, provide timestamps, exact delays, timeouts and periodic signals.

To keep the operating system apprised of the current time in the external world, typical systems use a high priority interrupt driven by an accurate clock at 100-1000 times per second. Most operating systems maintain a counter which gets updated every timer interrupt. The value of this counter, the timer tick counter, represents the number of timer ticks or interrupts that the system has seen since startup. Operating systems like  $\mu$ C/OS use this counter as the system clock. These operating systems offer a *current-time* function that returns the time as the number of ticks since the system

started. The granularity of this measurement is dependent on the frequency of the timer interrupt, and the user has to perform the conversion from ticks to the desired time units.

Other systems like Linux maintain the system time relative to the Epoch Jan. 1 1970 in terms of seconds and microseconds as opposed to timer ticks. In these cases, updates to the system clock involves adding a timer tick interval in seconds and microseconds to the system clock and handling possible microsecond overflows. As the overhead of this update is far greater than the simple counter increment approach, the timer interrupt handler is treated as a long interrupt. A typical 'long interrupt handler' in Linux splits the workload into work that needs to be done immediately and work that can be done a little later. The interrupt handler handles only the former and schedules the latter in what is termed as the bottom half of the interrupt. Thus, the timer interrupt handler in Linux only updates the timer tick counter. The system clock update takes place in the bottom half of the interrupt. To handle possible infrequent updates the system clock, Linux maintains an additional counter, the wall clock tick counter, which keeps track of the last update to the system clock in terms of timer ticks [26].

When asked for the *current-time*, Linux returns the value of the software system clock after accounting for the time that has elapsed since it was last updated. The elapsed time is comprised of two components. The first com-

ponent takes care of possible infrequent updates to the system clock. This is done by accounting for differences between the timer tick counter and the wall clock tick counter. The second component accounts for the time since the last timer interrupt. Computing this involves using counters that are updated independently by the hardware, like the timer modules count-down register. The timer module's countdown register value gives the amount of time remaining until the next timer interrupt. The operating system converts this value appropriately to compute the time elapsed since the last interrupt. In architectures with on-chip counters, like the Time Stamp Counter in Intel's microprocessors, Linux estimates the time since the last interrupt occurred by using the difference between the TSCs current value and its value at the last interrupt.

There are problems with each of these schemes. The simple interrupt-driven scheme is not scalable, as more frequent interrupts would simply increase the operating system's overhead and increase the chance that a high-priority clock interrupt would delay the execution of an otherwise high-priority task. Using the TSC counter or the timer counter registers in order to achieve finer granularities complicates the process of reading the system clock. The complexity of the operation can result in a substantial overhead that can effect the accuracy of the readings. This is the case when the overhead involved in obtaining the higher resolution measurement is of

the same order as the precision of the measurement itself. On the MCORE processor the Linux like scheme takes approximately 8 microseconds to complete assuming that there are no overheads involved in accessing the timer counter registers. Thus in the best case it is within 6% of the precision of the timer measurement. The accuracy of a time measurement that uses interpolation techniques is considered to be less accurate than one which is based exclusively on interrupt based clocks [Kailas2000]. In addition, this process of interpolation is extremely platform dependent and is not easily portable across systems.

Often a task in a real-time system has to pause its execution for a finite amount of time. This time is termed the timeout or delay. This delay value is typically expressed in the terms of system clock units. All operating systems provide facilities for tasks to place themselves on the timeout queue or delay queue or pause queue. Every timer interrupt, besides updating the system clock, the RTOS updates the state of tasks on this timeout queue. If the timeout value associated with the task has expired it is released and placed on the ready queue. By associating the timer interrupt with the timeout queue update, the granularity of time delays automatically gets restricted to that of the system clock. Typical embedded applications like those in networking and controls require granularities far finer than that of

the system clock timer interrupt which is typically 10 ms. Finer resolutions would imply an increase in the RTOS overhead.

One of the solutions to circumvent this problem has been to use hardware based timers to schedule individual tasks which require timing resolutions higher than those provided by the system clock.

Timer implementation is a POSIX 1004.3 standard. Several OSes offer this facility including Real - Time MACH [31], real-time extensions to Win NT, vxWorks[25] etc. This facility includes providing the task the capability to create individual timers. Each of these timers is associated with a period or one-shot timeout and an expiration action. Upon the creation of a timer the OS would program one of the multiple clocks (hardware counters which countdown and release an interrupt when they hit zero) based on the information provided by the task. When the timer throws an interrupt the associated interrupt handler takes the appropriate expiration action which normally involves releasing a task. Some RTOSes extend this single user task - single timer concept by associating multiple tasks with a timer. The timer is associated with a software based queue of tasks sorted on the basis of expiration time. This timer timeout queue is rather similar to the system level timeout queue. This timer mechanism is efficient when the number of tasks using it is low and the number of interrupts do not completely overwhelm the system.

One of the chief issues associated with any form of timeout queue is the overhead of maintaining it. Typically the timeout queue is maintained as some form of linked list structure. RTOSes like Echidna, NOS and realtime versions of Linux maintain the timeout queue as a queue of tasks sorted on the basis of their timeouts. The timeout of any task on the queue is relative to that of the task immediately before it on the queue. Insertion onto the queue has an overhead of O(n) while update is O(1) because only the timeout of the first element has to be updated. The complexity of removing tasks from the queue i.e. releasing a task after its timeout has expired is also an O(1) operation. But at an given update event, more than one task may become ready to run. Thus the total overhead associated with releasing tasks from the timeout queue is dependent on the number of tasks in the system. This chief advantage of this method is the low overhead associated with the update. The chief disadvantage of this scheme is the non-deterministic overhead.

$\mu$ C/OS tackles the problem of non-determinism associated with inserting a task on the timeout queue by eliminating the need to perform this operation completely. All the tasks in the system have an entry in the timeout queue by default but only some tasks have delays associated with them. Timeout queue updates require traversal of the entire queue and updating

the status of each individual entry. Though this operation has a high overhead, it is constant in a system with a fixed number of tasks.

## 2.2.3 Inter process Communication and Synchronization

Most operating systems provide a variety of facilities for two processes to exchange data, control information and synchronize this information exchange in order to ensure that it occurs at the right time and such that the two processes do not interfere with each other. Typical operating system methods for exchanging information include shared memory and message queues. Typical OS synchronization primitives include semaphores, mutexes and monitors.

As virtual memory is not a common feature among RTOSes, most uniprocessor RTOSes do not support shared memory. Shared memory in these systems is normally implemented in these systems as global data. In order to synchronize access to this global data synchronization primitives like semaphores and mutexes can be used. Sometimes the need for these synchronization mechanisms is eliminated by intelligently scheduling the processes accessing this data.

Message queues provide a means for one or many threads to communicate with some other thread or threads. Message queues can be implemented as FIFO or LIFO queues when all messages have the same priority

or as a list of messages sorted on the basis of priority. A mailbox is a message queue which can hold only one message at a given point.

Semaphores and mutexes are common synchronization primitives implemented in RTOSes. Each semaphore is associated with a count which keeps track of the number of tasks which can access some shared data at a given point.

The following are operations common across all IPC mechanisms.

When a task makes a request for a semaphore or a message on the message queue one of two things can happen. If the resource is available the task is granted its request right away. If it is not available the operating system places the task on the blocked list of tasks waiting for the particular resource.

Similarly when a task posts a semaphore or a message there are two possible events that can occur. If there is no task waiting for the resource than the operating system notes that an additional resource has been made available. On the other hand if there are tasks waiting on that resource than the OS selects a task from the list of waiting tasks to release. This selection policy can be either based on the order in which requests for the resource were made i.e. FIFO or based on priority i.e. the task with the highest priority is released every time or in a random fashion.

μC/OS offers various inter-process communication mechanisms including semaphores, message queues etc. Each mechanism is classified as a type of event and is associated with a data structure called the event block. Event blocks contain information like the nature of the event (semaphore etc.), an event counter, and a list of tasks blocked on the event (Blocked task list). This blocked list is similar to the RTOS' ready list. Blocking a task on a particular event involves updating the event's blocked list as well as removing it from the RTOS' ready list. Determining which task needs to be released upon the posting of an event involves a procedure similar to that of determining which task needs to be run. The overheads of these operations are constant. The disadvantage of this implementation is that each event is associated with its own blocked list and using an IPC heavy system will require high memory overheads.

Echidna on the other hand provides a synchronization primitive similar to the semaphore called the syncaphore. The blocked list of a syncaphore is a FIFO queue. Inserting a task on the queue has a complexity of O(n) in the current implementation as the OS traverses the entire queue of blocked tasks and adds the new entry to the end of queue. This can be optimized to an O(1) operation by maintaining an additional pointer to the tail of the queue. The task which is released when a syncaphore is posted is always the first task in the blocked queue. Task selection is thus a O(1) operation.

In Echidna the task blocks are moved between the various queues. Thus using many syncaphores does not increase the memory overhead of the operating system.

### 2.3 Related Work

A software based clock in general is susceptible to variations in the interrupt latency of the processor and the time to execute the timer interrupt handler. Various suggestions have been made to provide more accurate timing [31,32,20]. In particular, Savage [31] suggests using additional high resolution hardware timers. Each timer is associated with a sorted timeout queue onto which a task can add itself. The scheduler of the main operating system (Mach) is multiplexed with the interrupt handler of these hardware timers. The resolution in this scheme is achieved by increasing the interrupt overhead of the system. Kailas [20] focuses on building an on-chip time management unit that provides accurate and precise time readings. In their scheme the system time is updated independently of the software. The scheme's focus is to provide an accurate time stamp for events. Adomat [31] transfers the entire RTOS functionality into hardware in an attempt to get better determinism and performance. They suggest building a real time coprocessor unit to achieve this. The coprocessor is capable of making

scheduling decisions, etc. This does not translate into flexibility as far as the RTOS developer goes.

The off chip hardware unit is well suited for multiprocessing real time environments. Lindh [34] discusses incorporating the real time coprocessor into a multiprocessor environment. Klevin [35] also discusses using it for bus monitoring in a multi processor unit. Furuns [33] suggests hardware means to support asynchronous interprocess communication in a message intense system.

## CHAPTER 3

## **CCAM: DESCRIPTION**

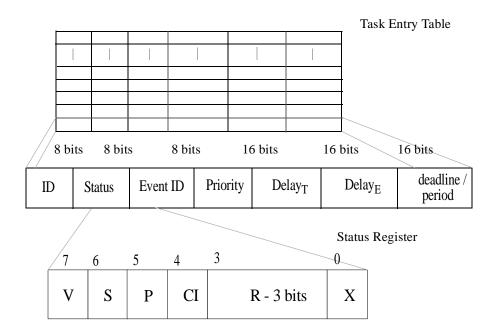

The CCAM is a hardware data structure that maintains the state of all the tasks running on the system. Figure 1 shows the layout of the CCAM Task Entry Table. We use a 64 entry CCAM table for our experiments. Each entry is 72 bits wide and has 6 fields.

### 3.1 CCAM Structure

Each task in the system is associated with an entry in the CCAM. The following are the fields in the CCAM.

**ID**: This field gives the address of the task entry in the CCAM table. It serves as the unique identifier for a task and is the value which the hardware uses to tag the result of any requested search.

**Status:** This 8 bit entry indicates the status of the associated task entry. The structure of the status entry is given in Fig 3.1. All the fields are single bit wide except for the Run Status field which is 3 bits wide.

42

Task Status Register Bit Descriptors

V - Valid CI - Cannot Interrupt

S - Suspend R - Run /Scheduling Status

P - Periodic Task X - Unused

Fig. 3.1. CCAM Structure. The structure of the CCAM's Task Entry Table is shown. Each individual task entry comprises of several fields which contain pertinent information for a task. The status, event id and priority are all 8 bit fields while the remaining fields are all 16 bits long.

**Valid:** This bit is used to indicate if the entry in the CCAM table has valid data or not.

**Suspend:** Setting this bit indicates that the task has been suspended.

**Periodic:** When this bit is set it indicates that the task is periodic in nature. The CCAM provides support for periodic tasks whose deadlines are the release times for the next iteration of the task.

**Cannot Interrupt:** Tasks with this bit set cannot generate CCAM interrupts when they become available to run.

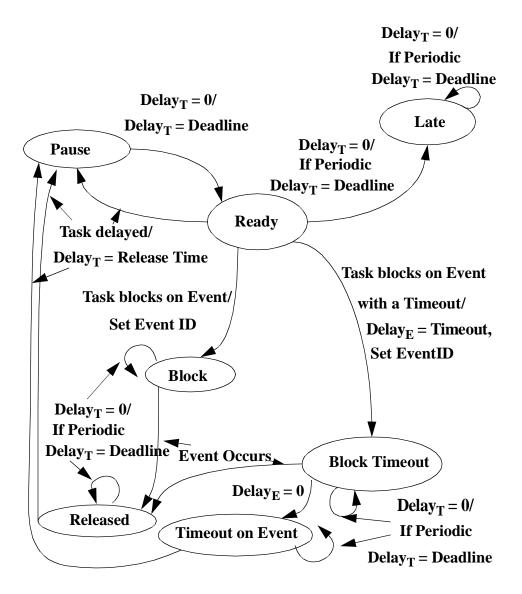

Fig. 3.2. State Machine representation of Run Status of a Task. The diagram shows how the run status of a task changes in the course of its execution. Each task is associated with a release time and a deadline. In the case of a periodic task the deadline is the period of the task.  $Delay_T$ ,  $Delay_E$  are the two types of delays possible for tasks. They are updated every timer tick. The former is mapped onto the Delay - Timeout field and the latter to the Timeout field.

**Run Status:** This 3 bit field is used to represent the scheduling status of the task. Tasks have a time related or event related status. Tasks may have any of the following time related status,

- Pause i.e. waiting to be released,

- Ready i.e. available for execution or

- Late i.e. has missed its deadline.

In addition a task may have event related status like

- · Blocked or waiting on an event,

- Blocked with a timeout i.e. waiting on an event for a finite amount of time,

- Released i.e. becoming available to run after the event is posted and

- Released after timing out on an event.

Fig3.2 shows how the run status of the task changes during the course of its execution.

These states are equivalent to the various queues maintained by the OS to help manage tasks. For example a task which is available for execution is associated with a ready status which is the same as being placed on a ready queue. Tasks which are waiting on an event are placed on the blocked queue associated with the particular event. The various event queues are

**Table 1: CCAM Module Address Map**

| Address  | Name                       | Use                                                                                        | Access<br>Type  |

|----------|----------------------------|--------------------------------------------------------------------------------------------|-----------------|

| 100010e0 | ID Register                | Task ID on which operation needs to be per-<br>formed; Holds results of a CCAM Instruction | Read /<br>Write |

| 100010e4 | Instruction Regis-<br>ter  | CCAM Instruction and required data are written into it                                     | Write           |

| 100010e8 | CCAM Tick Data<br>Register | Duration of single tick in microseconds                                                    | Write           |

| 100010ea | CCAM Tick Register         | Number of system ticks which have occurred since initialization                            | Read/Write      |

| 100010ee | Control Register           | Used for configuring the CCAM operation mode                                               | Read/Write      |

integrated on the CCAM. All blocked tasks are given the status of blocked or blocked with a timeout. The event ID is used to help determine which event queue a task is on.

**Priority:** This 8-bit field holds the priority of a task as per operating system convention. This value is used to by the Get Task- Priority Sort instruction and also to break ties when an event on which two or more tasks are waiting on is released.

**Event ID:** This field holds the ID of the event on which a task is waiting. It helps distinguish between all blocked tasks in the system.

**Delay Fields:** There are totally three 16-bit fields in a CCAM entry which are dedicated to handling time related constraints.

• **Delay**<sub>T</sub> This 16 bit field holds either an unsigned or signed value depending on the CCAM configuration. Negative delay values indicate that the timeout value has expired. The delay values are updated every time the timeout queue is updated. In the case of preemptive systems this is every timer tick while for a non preemptive systems this would be when a task has relinquished the processor and a timeout queue update needs to be performed or every timer tick if the system is idling.

The interpretation of the value in this field depends on the run status of the task. When the task in paused the value in this field represents the release time of the task. Once the task is ready to run, the value in the field would represent the deadline for the task. When the CCAM is configured to support negative delays, the delay field will continue to be updated once the deadline has passed and the task's status has changed to late. The delay value then indicates how late the task is.

In the case of periodic tasks the value in this field represents the release time for the next iteration of the task. If the periodic task is ready it also represents the relative deadline of the current iteration of the task.

- Delay<sub>E</sub> This value is used to track event timeout values. When a task

blocks on an event it can specify the maximum amount of time in timer

ticks that it is willing to wait for the event. The CCAM puts this value in

this delay field.

- Periodic Delay / Deadline This 16 bit location serves as a storage

location. When an EDF scheduler is used it is used to store the value of

the deadline of the task. When the task is released i.e the delay<sub>T</sub> field

reaches zero, it is this value which gets automatically loaded into the

delay<sub>T</sub> field. For a periodic task this value represents the period of the

task.

### 3.2 CCAM Module Interface

The CCAM module interface has 5 registers. These registers are mapped into the memory space of the system and can be accessed using load and store instructions. The memory module map of the CCAM interface is given in Table 1.

**CCAM Control Register:** This 8 bit register is used to configure the operating mode of the CCAM.

The bits have the following meaning

Auto Decrement AD When this bit is set the CCAM automatically updates the state of the delays every "timer tick" i.e. performs automatic timeout queue maintenance. The RTOS sets the rate of the timer tick at initialization.

Enable Interrupt EI When this bit is set along with the AD bit the CCAM generates interrupts every time it performs a timeout queue update and finds that a task has become available for execution i.e. status of any of the tasks in the CCAM table has changed from Pause to Ready or from Blocked Timeout to Released Timeout following an update.

Enable Repetitive Interrupt ERI When only the EI bit is set the CCAM interrupt is a one-time interrupt. Enabling this bit makes the CCAM interrupt a repetitive one.

Lock L When this bit is set the CCAM cannot perform any automatic updates. The RTOS sets this bit every time it wants to access the CCAM and the AD mode is enabled.

Negative Delay ND This bit determines if the CCAM delay is a signed or unsigned number. When set delay values of tasks, which are late or have been released following timeout on an event, will continue to be decremented during timeout queue updates.

Release Time - Deadline RD When this bit is set it implies that the RTOS uses both release time and deadline information to perform its scheduling.

This mode is useful in deploying dynamic priority based RTOSes onto the CCAM.

At startup all bits in the control register are disabled. The CCAM operating mode is normally set up during system initialization. The configuration choice is made based on whether the system is preemptive or nonpreemptive, how many tasks it is running, the nature of its scheduling algorithm etc. For example an operating system like Echidna would set the RD bit to indicate that tasks have a release time and a deadline.

The operating system uses two registers to access the information in the CCAM. These registers are the CCAM ID register and the CCAM Instruction Register.

**CCAM ID Register:** This register holds the id of the task which the next CCAM instruction works on. The ID for a 64 entry table is a number between 0 and 63 and is the index of the task's entry in the table. The CCAM returns information regarding the status of the last operation to the operating system via this register.

CCAM Instruction Register: The OS uses this register to load the CCAM instruction. Writing to this register initiates a CCAM operation.

The CCAM has 15 valid instructions of which 10 operate on specified CCAM task entries while the remaining 3 access every valid task entry in

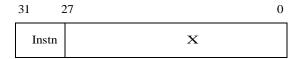

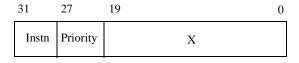

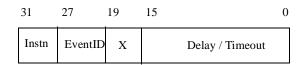

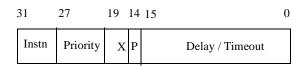

Format 1: Instructions with no data e.g. Priority and Delay Sort

| 31    | 27 | 15              | 0 |

|-------|----|-----------------|---|

| Instn | X  | Delay / Timeout |   |

Format 2: CCAM Tick, Set Delay Instructions - 16 bit Data

Format 3: Set Priority and Remove Task

Format 4: Set Event Instruction

Format 5: Create Task Instruction

Fig. 3.3. Instruction Layout of CCAM instructions. This figure represents the interpretation of the different bits in a CCAM instruction word.

the CCAM. Issuing a CCAM instruction in majority of the cases is a two step procedure. In the first step, the operating system writes the index of the task on which the instruction is being performed into the CCAM ID register. Following this it writes the instruction into the CCAM Instruction Reg-

Table 3: State Assignments for Run Status

| State           | Assignment |

|-----------------|------------|

| Pause           | 000        |

| Ready           | 100        |

| Late            | 101        |

| Block           | 010        |

| Block Timeout   | 011        |

| Release         | 110        |

| Release Timeout | 111        |

|                 |            |

ister. The CCAM performs the operation and returns the result of the operation via the CCAM ID register. For example, when the OS issues a release event operation, the CCAM returns the id of the task that was made ready to run. Details of the instructions and their operations are given in Table 2. A layout of the different types of instructions is given in Figure 3.3.

The instructions occupy the upper 4 bits of the CCAM instruction word. The remaining 28 bits are used to pass extra information required to execute the instruction to the CCAM. For example, during task creation, information regarding the task - its periodic nature, its priority are all packed in the CCAM instruction word.

**Table 2: CCAM Instructions**

| Instruction                        | Use                                                                                                                                                            |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Create Task                        | Creates a task entry at a specified CCAM slot;<br>Information regarding a tasks periodicity, priority,<br>interrupt status are passed in the instruction word. |

| Delete Task                        | Invalidates the associated task entry                                                                                                                          |

| Set priority                       | Sets the priority of the specified task                                                                                                                        |

| Get priority                       | Returns the priority of specified task                                                                                                                         |

| Set Suspend                        | Sets suspend flag of task based on value passed                                                                                                                |

| Get Status                         | Returns the Status Register Value of specific task                                                                                                             |

| Set Delay:<br>Release Time         | Sets the Release Time for the specified task                                                                                                                   |

| Set Delay:<br>Relative<br>Deadline | Sets the relative deadline of a specified task or its period in the case of a periodic task                                                                    |

| Get Delay                          | Returns the delay value in the delay1 field. This value is either the                                                                                          |

| Set Event                          | Blocks the task on specified event; Updates the delay field of task with event timeout value                                                                   |

| Release Event                      | Searches for task with highest priority waiting on specified event id and releases it                                                                          |

| CCAM Tick                          | Decrements all the delay values associated with valid task entries and updates their status appropriately                                                      |

| Get Task -<br>Priority Sort        | Returns the task ID of the highest priority task which is ready to run                                                                                         |

| Get Task<br>Delay Sort             | Returns the ID of the first task with the least delay (delay 1 field) which is ready to run                                                                    |

**CCAM Time Tick Data Register:** This register specifies the duration of a single CCAM tick. The value of the time is given in hundreds of microseconds.

**CCAM Time Tick Register:** This register serves as the periodic time source for systems using the CCAM for timeout queue management. The register is a counter that is incremented every CCAM tick. The operating system can reset this value during runtime.

# 3.3 Implementation

**Run Status State Machine:** The run status of each task can be implemented as a state machine with 7 states. Each state is associated with 3 bits. The state machine flow is given in Figure 3.2. The individual state assignments are given in Table 3.

The inputs to the state machine are the following signals

Status. Periodic - This bit indicates if the task is periodic or not.

Set Event This signal goes high when a task is made to wait on an event i.e. a Set Event instruction is executed.

Set  $Delay_E$  This signal goes high when a value is loaded into the  $Delay_E$  field.

Set  $Delay_T$  This signal goes high when a value is loaded into the  $Delay_T$  field i.e. a Set Delay: Release Time Instruction is executed.

## Selection Logic Cell