### ABSTRACT

Title of dissertation: BUFFER-ON-BOARD MEMORY SYSTEM

Elliott Cooper-Balis,

Doctor of Philosophy, 2012

Dissertation directed by: Professor Dr. Bruce Jacob

Dept of Electrical & Computer Engineering

The design and implementation of the commodity memory architecture has resulted in significant limitations in a system's speed and capacity. To circumvent these limitations, designers and vendors have begun to place intermediate logic between the CPU and DRAM. This additional logic has two functions: to control the DRAM and to communicate with the CPU over a fast and narrow bus. The benefit provided by this logic is a reduction in pin-out to the memory system from the CPU and increased signal integrity seen by the DRAM, granting faster clock rates while increasing capacity. This new design is reminiscent of the FB-DIMM memory system yet makes key changes to its architecture including the use of existing DIMMs to reduce cost, a reduction in power (relative to FB-DIMM), and a more stable request latency. The problem is that the few vendors utilizing this design have the same general approach, yet the implementations vary greatly in their non-trivial details.

A hardware verified simulation suite is developed to accurately model and evaluate the behavior of this buffer-on-board memory system. A study of this design space is performed to determine optimal use of the resources involved. This includes DRAM and bus organization, queue storage, and mapping schemes. Various constraints based on implementation costs are placed on simulated configurations to confirm that these optimizations apply to viable systems. Finally, full system simulations are performed with MARSSx86 to better understand how this memory system interacts with a CPU, cache, and operating system executing an application. Full system simulations uncover behaviors not present in simple limit-case simulations such as the impact of address and channel mapping schemes or the organization of ports and the associated buffers. When applying insights gleaned from these simulations, optimal performance can be achieved while still considering outside constraints (i.e., pin-out, power, and fabrication costs).

# BUFFER-ON-BOARD MEMORY SYSTEM

by

# Elliott Cooper-Balis

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2012

# Advisory Committee:

Professor Dr. Bruce Jacob, Chair/Advisor

Professor Dr. Manoj Franklin

Professor Dr. Gang Qu

Professor Dr. Alan Sussman

Professor Dr. Donald Yeung

©Copyright by

Elliott Cooper-Balis 2012

This dissertation is dedicated to,

my family, Judith Cooper, Frank Balis, and Will Cooper-Balis

and

$Paul\ Rosenfeld$

For their help and support along the way

# Contents

| 1 | Bac | ekground                                    | 1  |  |

|---|-----|---------------------------------------------|----|--|

|   | 1.1 | Introduction                                | 1  |  |

|   | 1.2 | 1.2 Past, Present and Future Memory Systems |    |  |

|   |     | 1.2.1 Double Data Rate Synchronous DRAM     | 5  |  |

|   |     | 1.2.2 Registered & Load Reducing DIMM       | 12 |  |

|   |     | 1.2.3 Fully Buffered DIMM                   | 14 |  |

|   |     | 1.2.4 IBM Power 7                           | 17 |  |

|   |     | 1.2.5 Intel Scalable Memory Interface       | 19 |  |

|   |     | 1.2.6 AMD G3 Memory Extender                | 21 |  |

| 2 | Buf | fer-On-Board Memory System                  | 23 |  |

|   | 2.1 | Architecture Overview                       | 24 |  |

|   | 2.2 | Main BOB Controller                         | 26 |  |

|   | 2.3 | Simple Controller                           | 28 |  |

|   | 2.4 | Packets                                     | 31 |  |

| 3 | во  | B Simulation Suite                          | 33 |  |

|   | 3.1 | Simulation Framework                        | 33 |  |

|   | 3.2 | Hardware Verification                       | 35 |  |

| 4 | Sim | nulation Results                            | 38 |  |

|   | 4.1 | Limit-Case Simulations                      | 39 |  |

|   |     | 4.1.1 Simple Controller & DRAM Efficiency   | 40 |  |

| 6 | Apr | oendix  | A                                     | 154 |

|---|-----|---------|---------------------------------------|-----|

|   | 5.1 | Future  | Work                                  | 152 |

| 5 | Con | clusior | 1                                     | 148 |

|   |     | 4.2.5   | Port Parameters & Heuristics          | 132 |

|   |     | 4.2.4   | Read Return Queue                     | 120 |

|   |     | 4.2.3   | Address Mapping                       | 101 |

|   |     | 4.2.2   | Latency Analysis                      | 93  |

|   |     | 4.2.1   | System Performance & Power Trade-offs | 84  |

|   | 4.2 | Full Sy | stem Simulations                      | 81  |

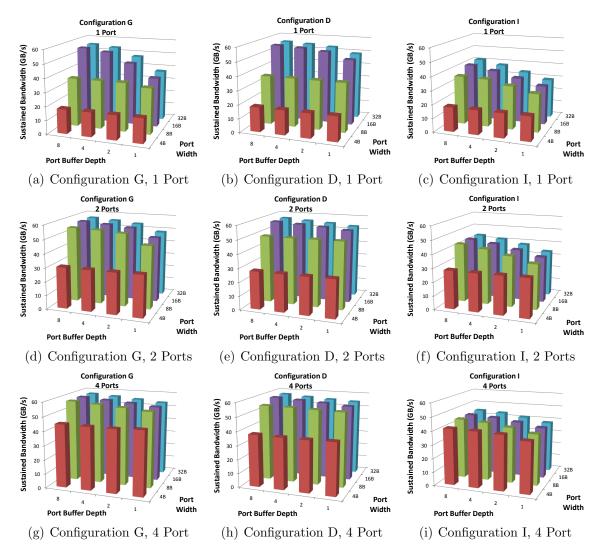

|   |     | 4.1.6   | Ports                                 | 76  |

|   |     | 4.1.5   | Cost Constrained Simulations          | 72  |

|   |     | 4.1.4   | Multi-Channel Optimization            | 58  |

|   |     | 4.1.3   | Peak Possible Bandwidth               | 56  |

|   |     | 4.1.2   | Link Bus Configuration                | 47  |

# List of Figures

| 1  | DRAM Signal Integrity Degradation        | 3  |

|----|------------------------------------------|----|

| 2  | Trends In Commodity DRAM                 | 4  |

| 3  | Modern DRAM Device                       | 7  |

| 4  | JEDEC DDR Memory System                  | 10 |

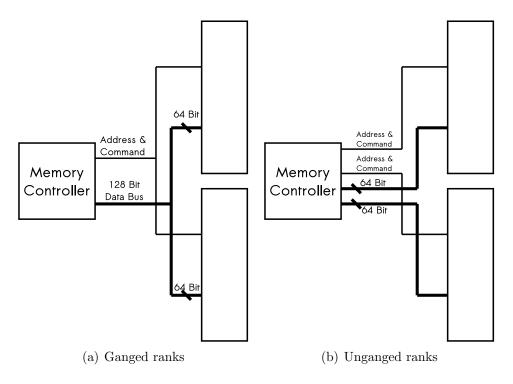

| 5  | Ganged vs. Unganged Memory               | 12 |

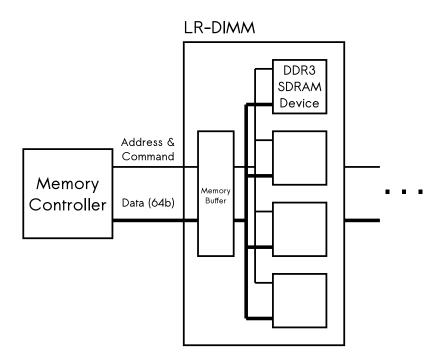

| 6  | LR-DIMM                                  | 14 |

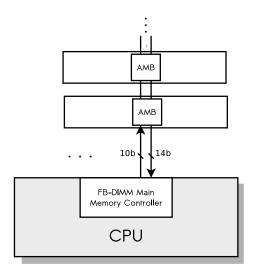

| 7  | FB-DIMM Memory Architecture              | 16 |

| 8  | IBM Power7 Memory Architecture           | 19 |

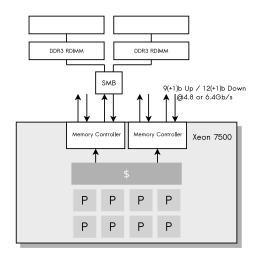

| 9  | Intel SMI/SMB Architecture               | 20 |

| 10 | AMD G3MX                                 | 22 |

| 11 | BOB Memory Architecture                  | 25 |

| 12 | Main BOB Controller                      | 27 |

| 13 | Simple Controller                        | 29 |

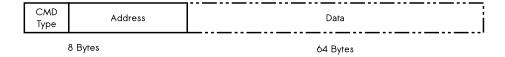

| 14 | BOB Packet Definition                    | 31 |

| 15 | ModelSIM Verification                    | 36 |

| 16 | ModelSIM In Action                       | 37 |

| 17 | Varying Rank Depth                       | 41 |

| 18 | Varying O–O–O Depth                      | 42 |

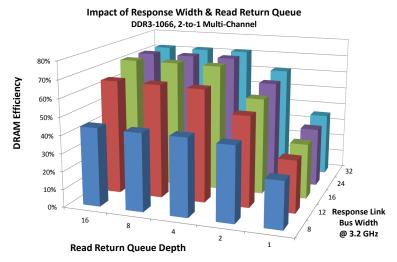

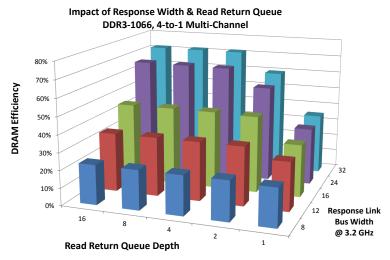

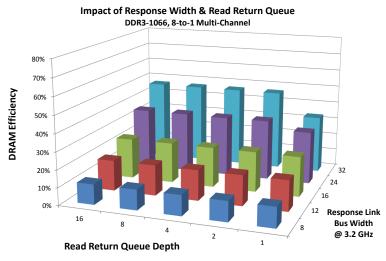

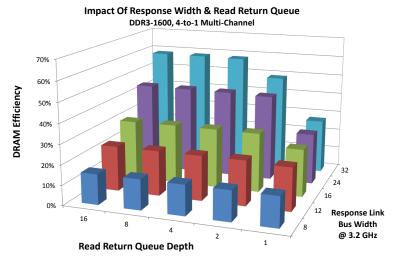

| 19 | RRQ Depth and Response Width - DDR3-1066 | 44 |

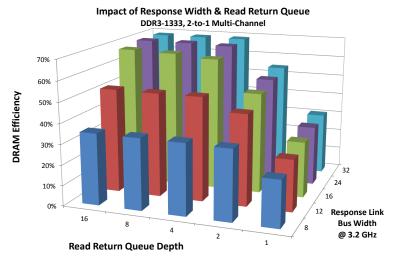

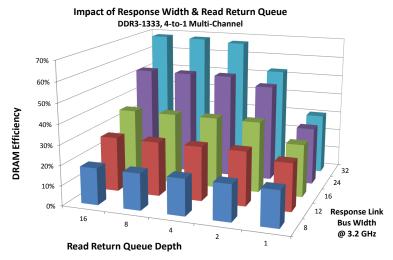

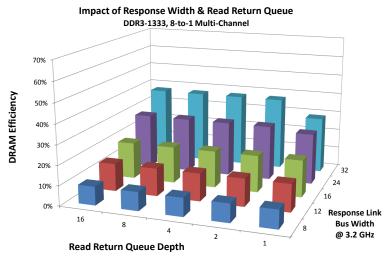

| 20 | RRQ Depth and Response Width - DDR3-1333 | 44 |

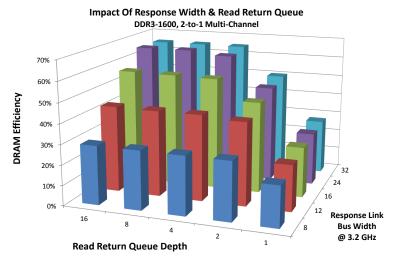

| 21 | RRQ Depth and Response Width - DDR3-1600 | 45 |

| 22 | Varying Response Link Bus                                          | 46 |

|----|--------------------------------------------------------------------|----|

| 23 | Impact of tFAW on Data Burst                                       | 47 |

| 24 | Link Bus Configurations - DDR3-1066                                | 50 |

| 25 | Link Bus Configurations - DDR3-1333                                | 51 |

| 26 | Link Bus Configurations - DDR3-1600                                | 51 |

| 27 | Impact of Read–Write Mix on Performance                            | 54 |

| 28 | Latency Components in Different BOB Configurations                 | 55 |

| 29 | Varying Number of BOB Channels                                     | 57 |

| 30 | Multi-Channel Arbitration                                          | 59 |

| 31 | 4-to-1 Multi-Channel Configuration                                 | 61 |

| 32 | Multi–Channel Bandwidth with DDR3-1066                             | 62 |

| 33 | Multi–Channel Bandwidth with DDR3-1333                             | 63 |

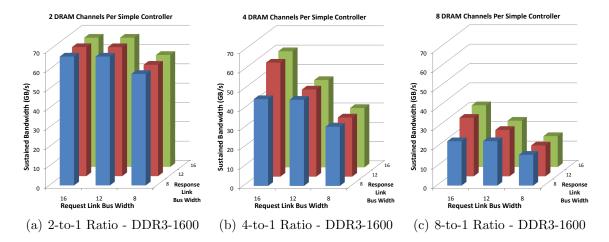

| 34 | Multi–Channel Bandwidth with DDR3-1600                             | 64 |

| 35 | Read Return Queue In Multi-Channel Configurations - DDR3-1066 $$ . | 69 |

| 36 | Read Return Queue In Multi-Channel Configurations - DDR3-1333 $$ . | 70 |

| 37 | Read Return Queue In Multi-Channel Configurations - DDR3-1600 $$ . | 71 |

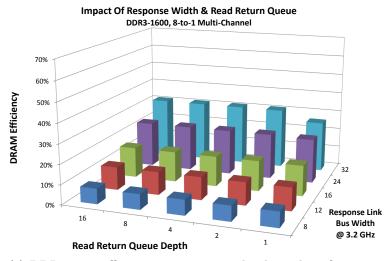

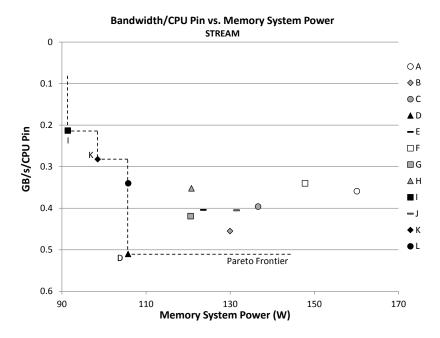

| 38 | Pareto Frontier Analysis                                           | 74 |

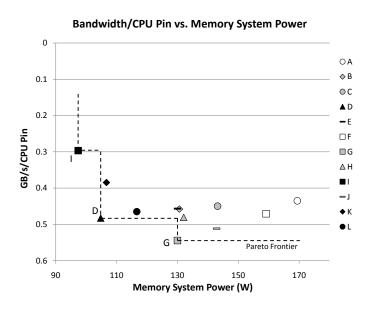

| 39 | Varying Port Width and Depth                                       | 78 |

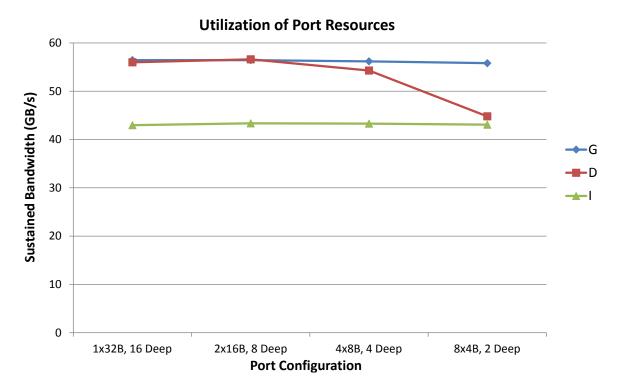

| 40 | Utilization of Port Resources                                      | 80 |

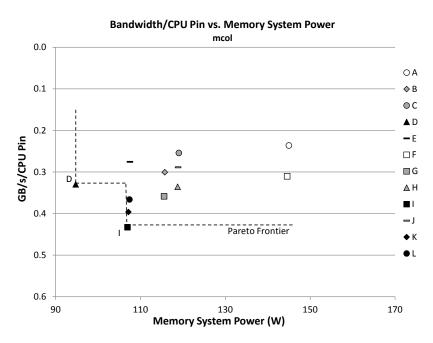

| 41 | Pareto Frontier Analysis - mcol                                    | 82 |

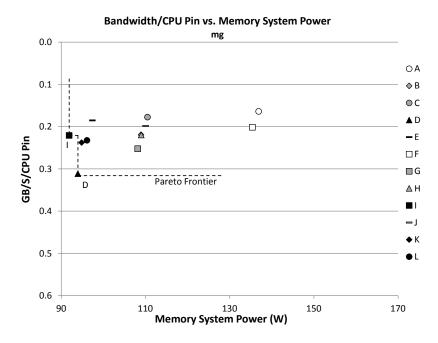

| 42 | Pareto Frontier Analysis - mg                                      | 83 |

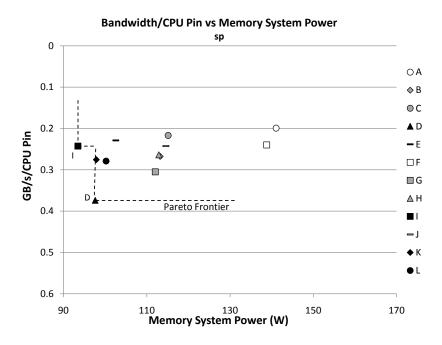

| 43 | Pareto Frontier Analysis - sp                                      | 83 |

| 44 | Pareto Frontier Analysis - STREAM                                  | 84 |

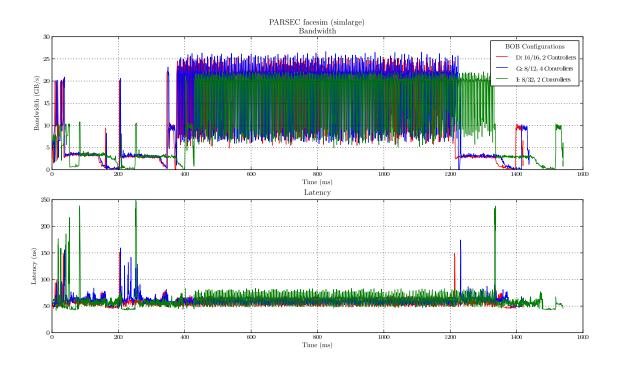

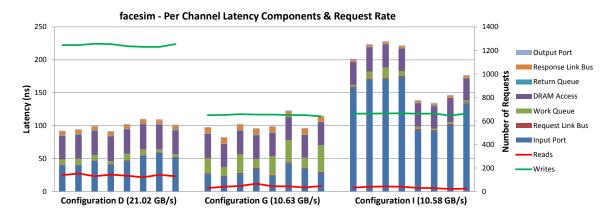

| 45 | Full System Simulation - facesim              | 88  |

|----|-----------------------------------------------|-----|

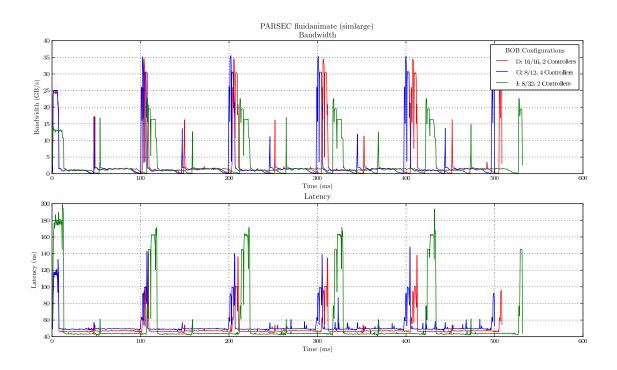

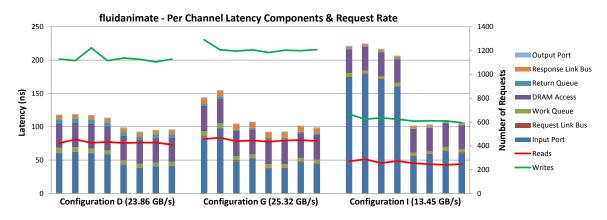

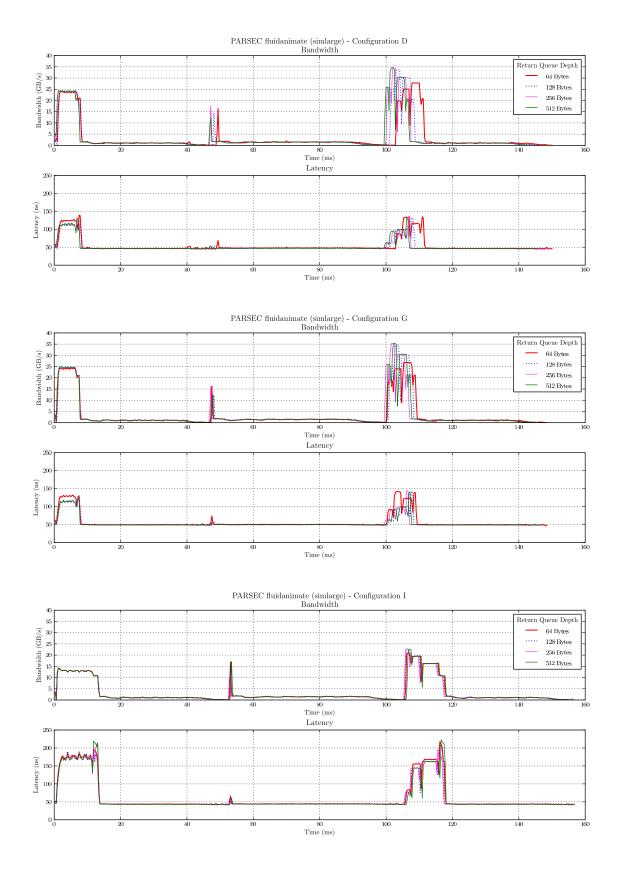

| 46 | Full System Simulation - fluidanimate         | 89  |

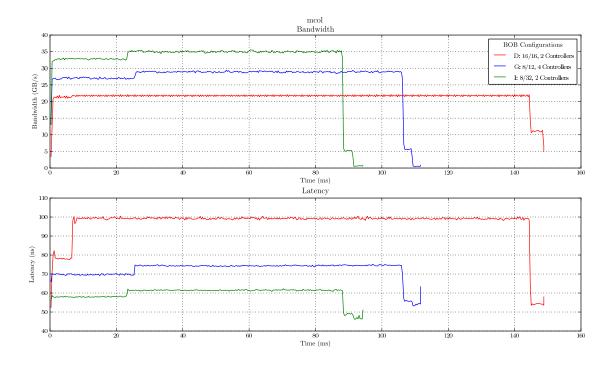

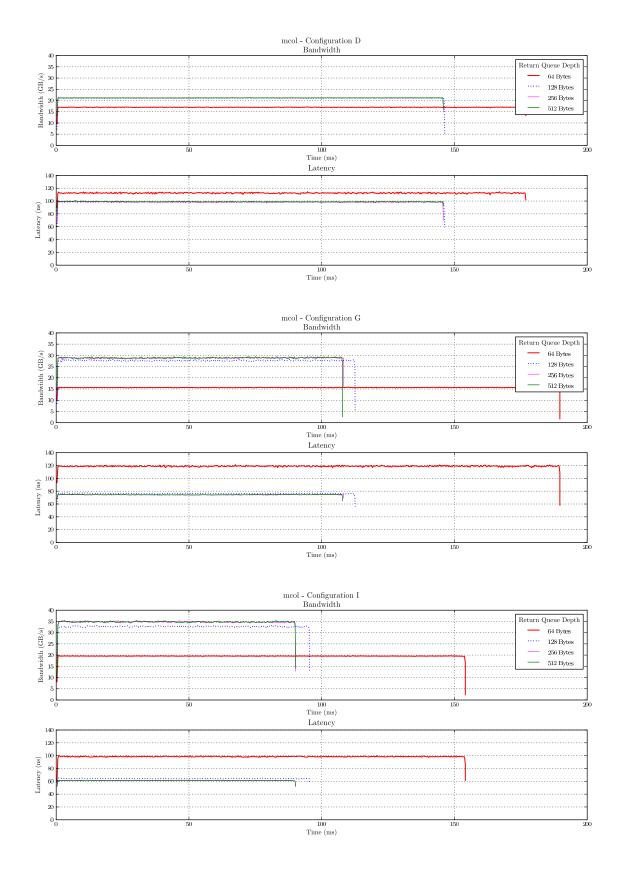

| 47 | Full System Simulation - mcol                 | 89  |

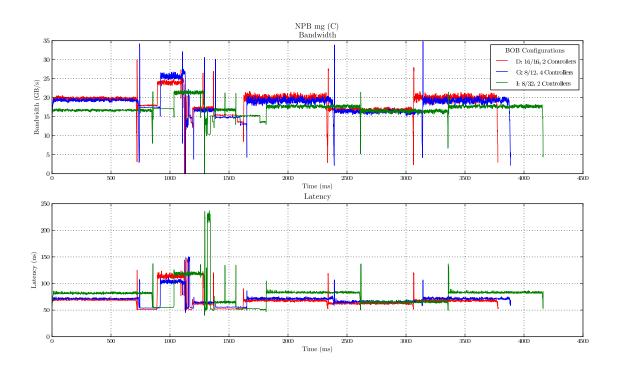

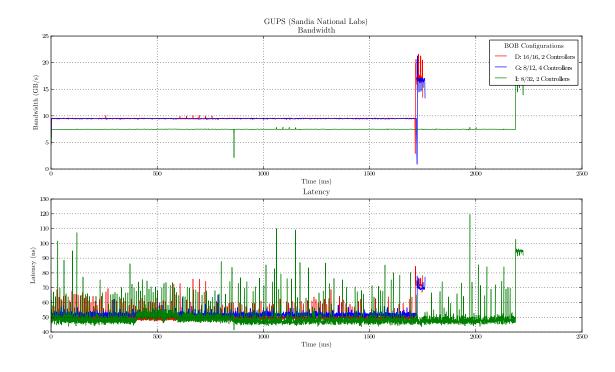

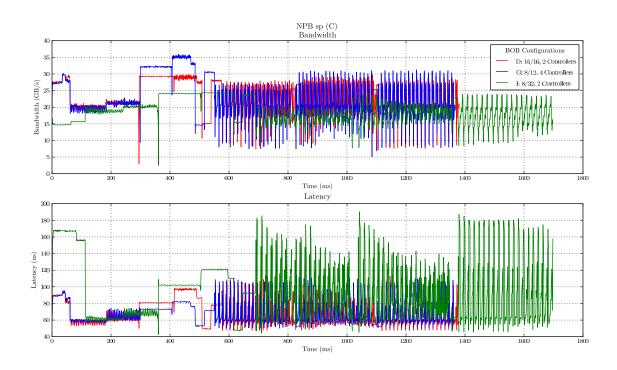

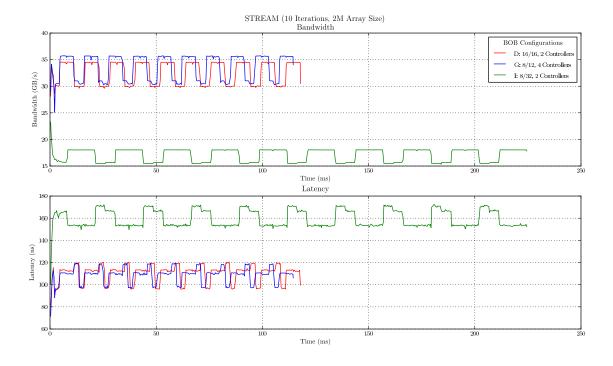

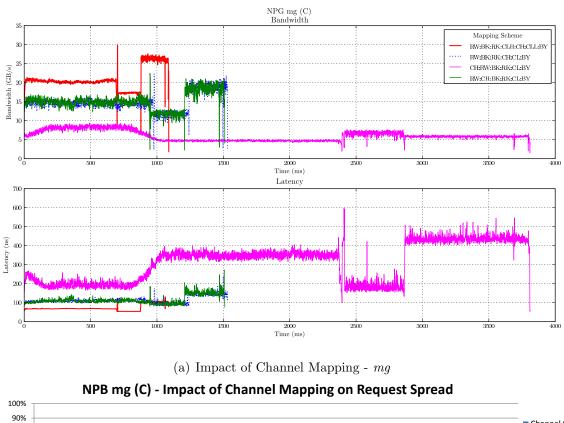

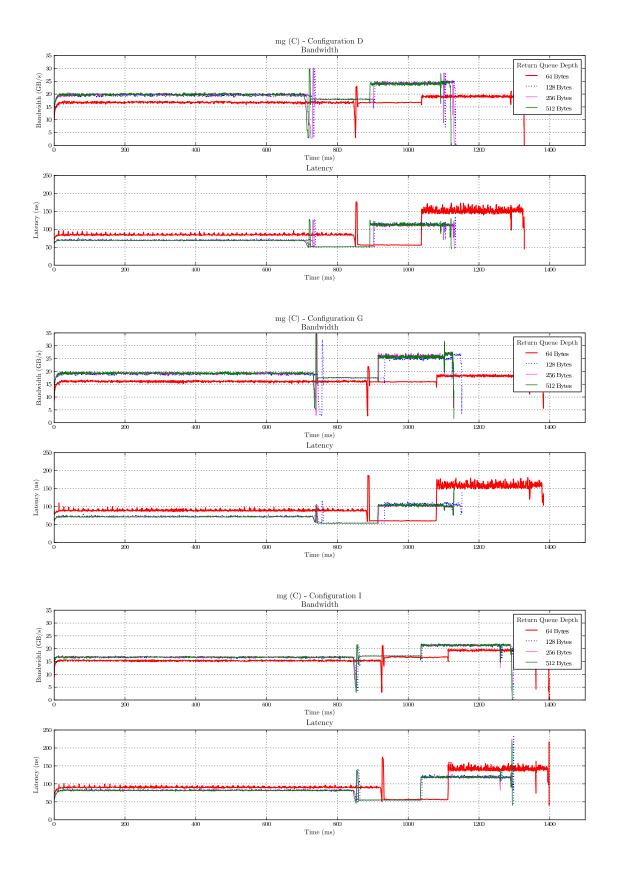

| 48 | Full System Simulation - mg                   | 90  |

| 49 | Full System Simulation - Sandia GUPS          | 90  |

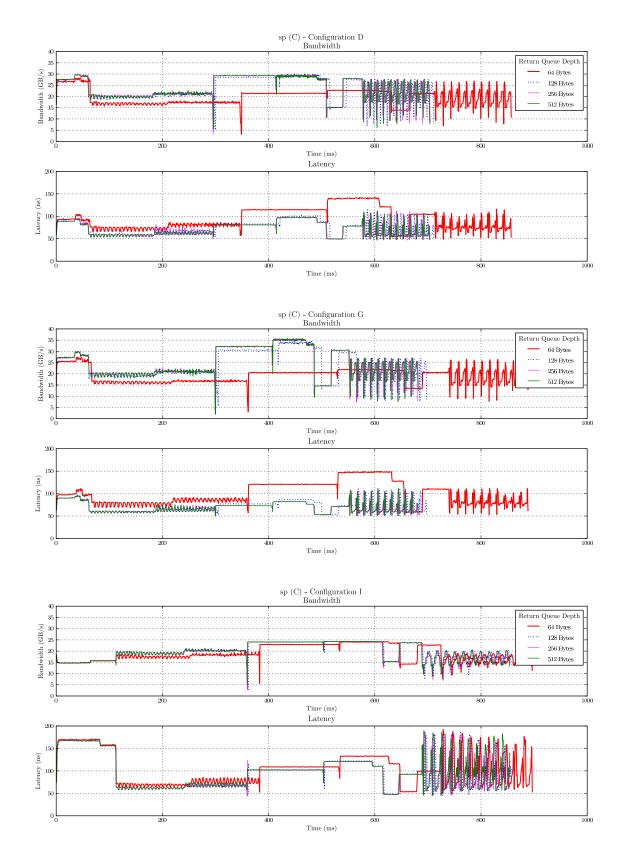

| 50 | Full System Simulation - sp                   | 91  |

| 51 | Full System Simulation - STREAM               | 91  |

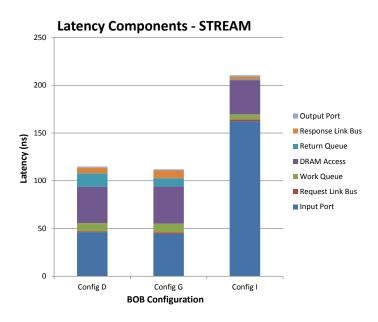

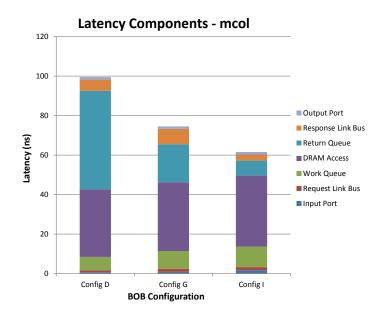

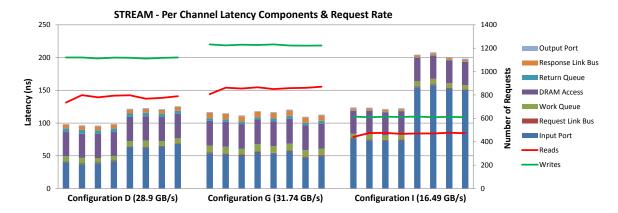

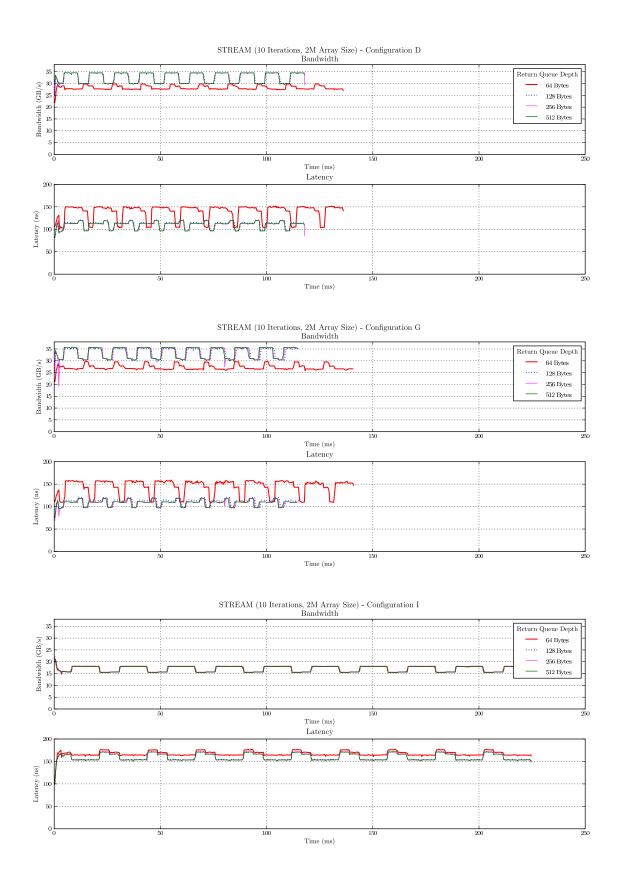

| 52 | Latency Components - STREAM                   | 94  |

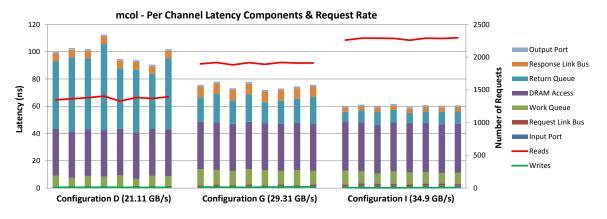

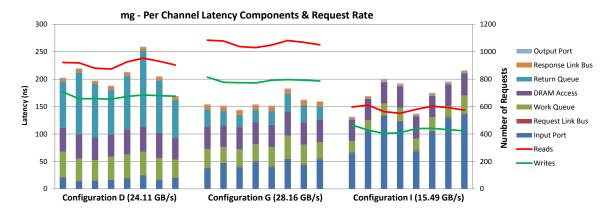

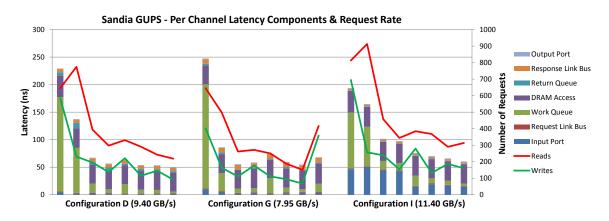

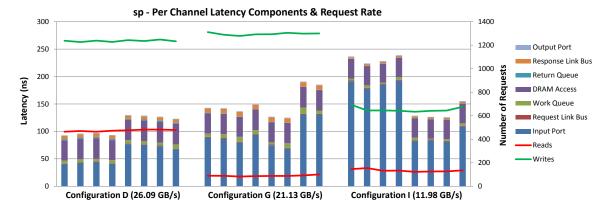

| 53 | Latency Components - $mcol$                   | 95  |

| 54 | Per Channel Latency Components - facesim      | 99  |

| 55 | Per Channel Latency Components - fluidanimate | 99  |

| 56 | Per Channel Latency Components - mcol         | 99  |

| 57 | Per Channel Latency Components - mg           | 100 |

| 58 | Per Channel Latency Components - Sandia GUPS  | 100 |

| 59 | Per Channel Latency Components - sp           | 100 |

| 60 | Per Channel Latency Components - STREAM       | 101 |

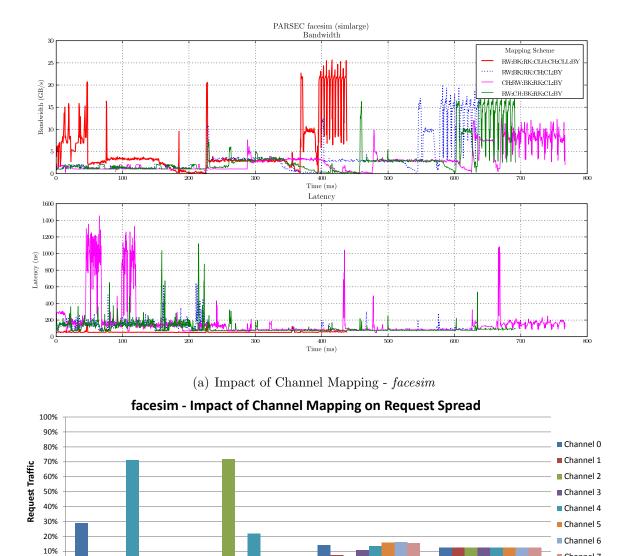

| 61 | Impact of Channel Mapping - facesim           | 106 |

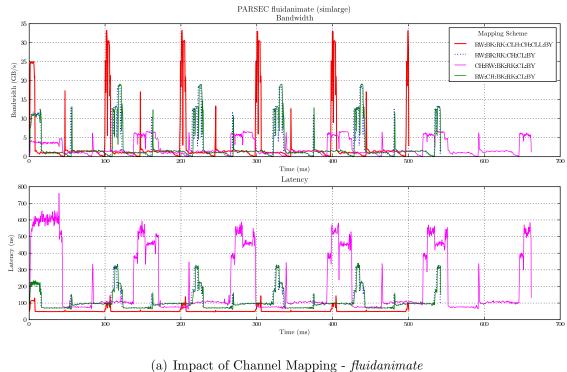

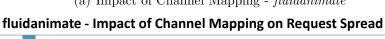

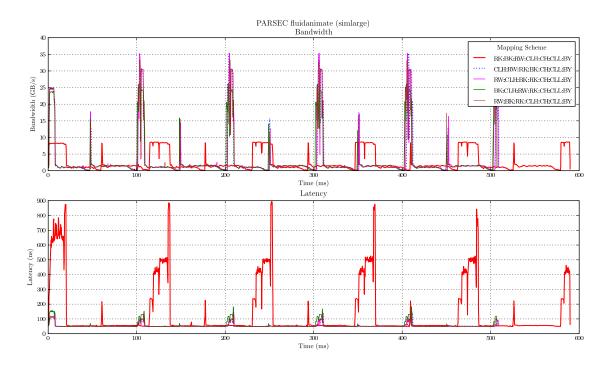

| 62 | Impact of Channel Mapping - fluidanimate      | 107 |

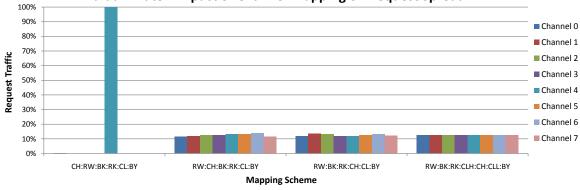

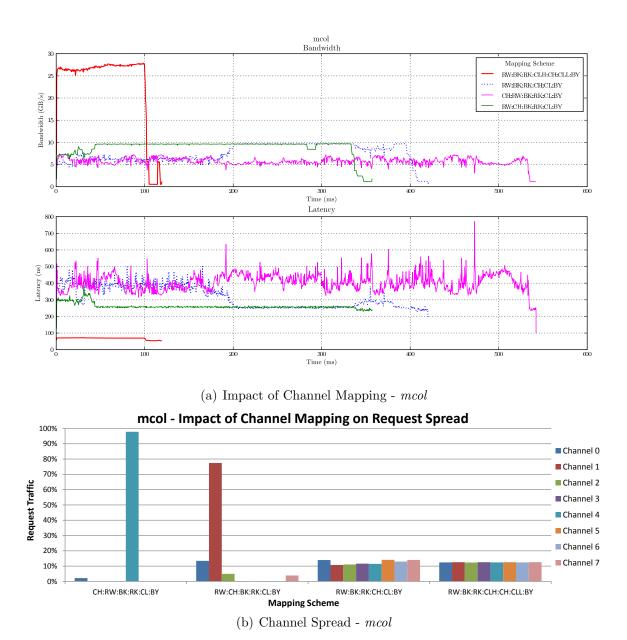

| 63 | Impact of Channel Mapping - $mcol$            | 108 |

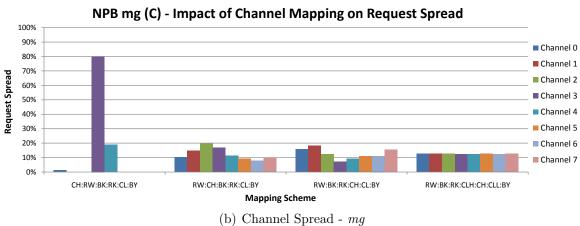

| 64 | Impact of Channel Mapping - mg                | 109 |

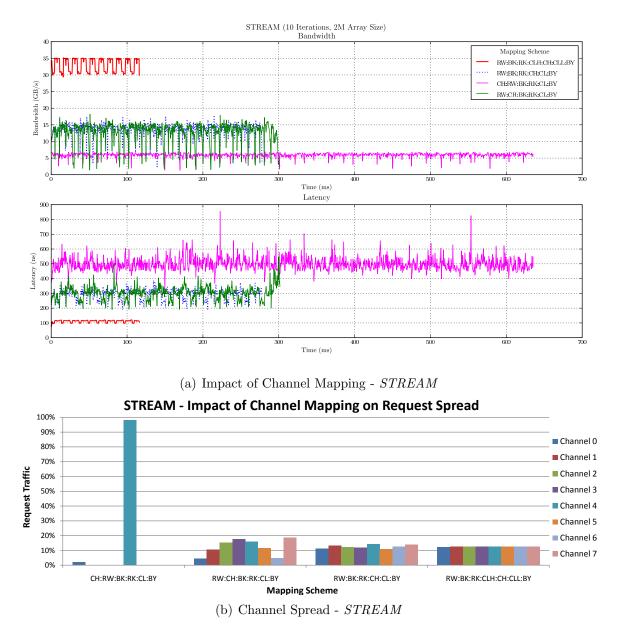

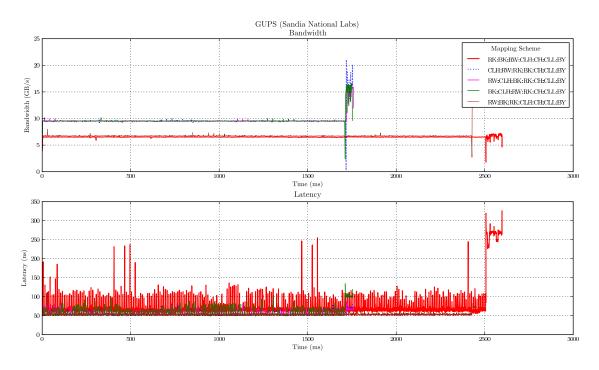

| 65 | Impact of Channel Mapping - STREAM            | 110 |

| 66 | Address Mapping - fluidanimate                | 115 |

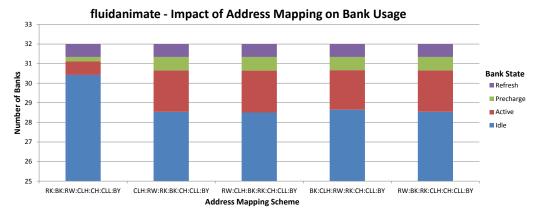

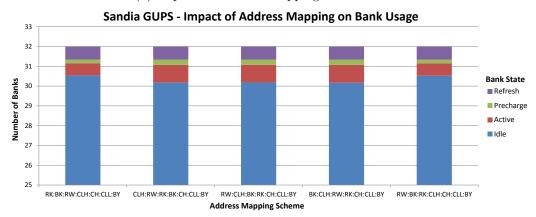

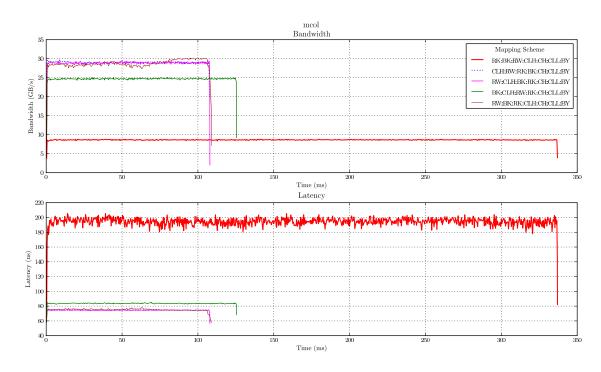

| 67 | Address Mapping - Sandia GUPS                 | 116 |

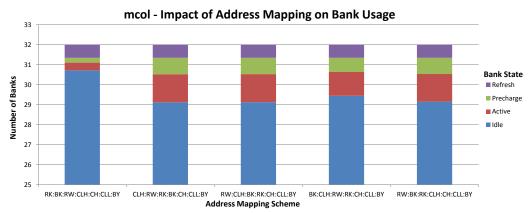

| 68 | Address Mapping - $mcol$                    | 117 |

|----|---------------------------------------------|-----|

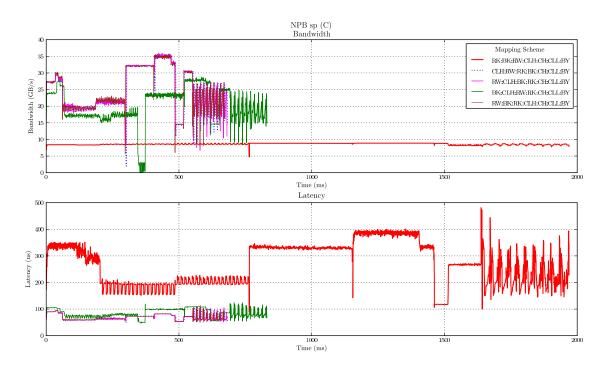

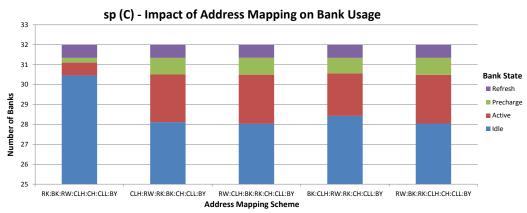

| 69 | Address Mapping - $sp$                      | 118 |

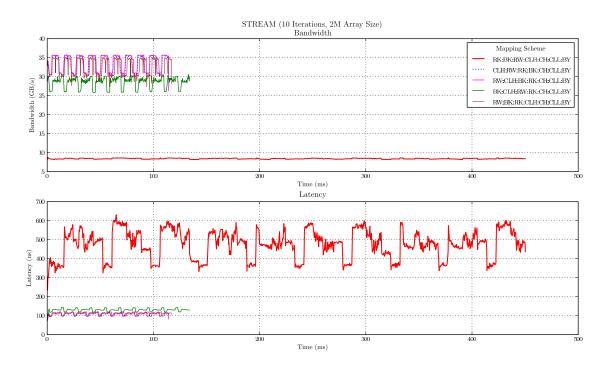

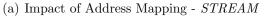

| 70 | Address Mapping - STREAM                    | 119 |

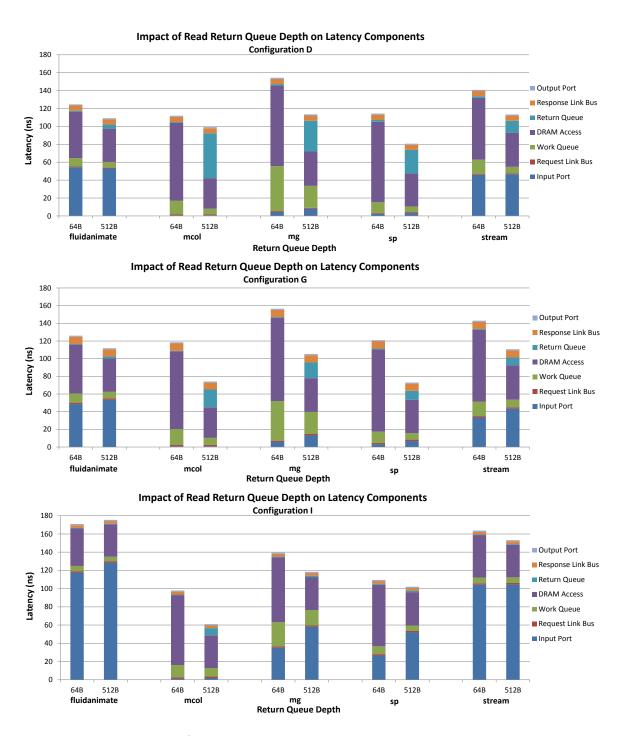

| 71 | Impact of Return Queue Depth - fluidanimate | 123 |

| 72 | Impact of Return Queue Depth - $mcol$       | 124 |

| 73 | Impact of Return Queue Depth - $mg$         | 125 |

| 74 | Impact of Return Queue Depth - $sp$         | 126 |

| 75 | Impact of Return Queue Depth - $STREAM$     | 127 |

| 76 | Impact of Return Queue on Latency           | 129 |

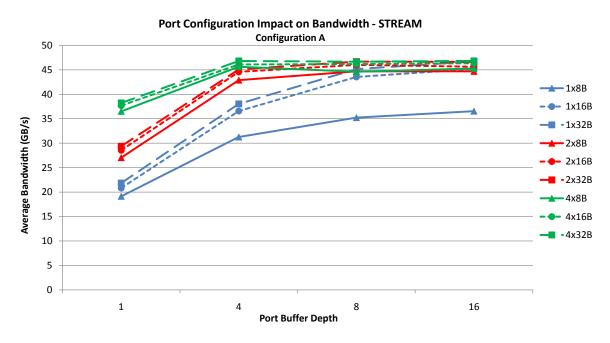

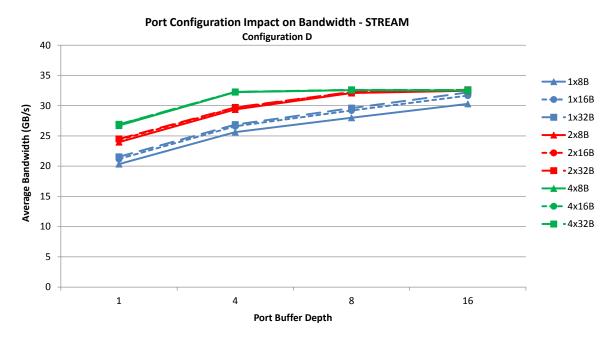

| 77 | Impact of Port Configuration - $STREAM$ (A) | 136 |

| 78 | Impact of Port Configuration - $STREAM$ (D) | 137 |

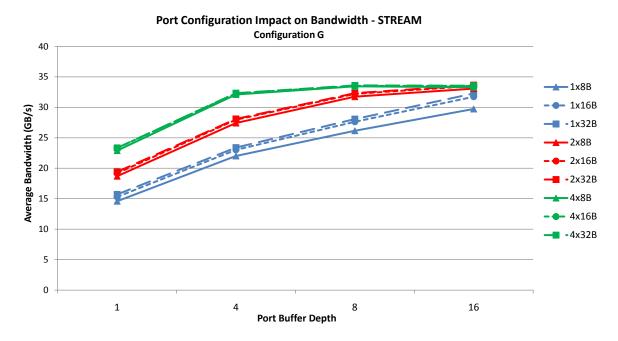

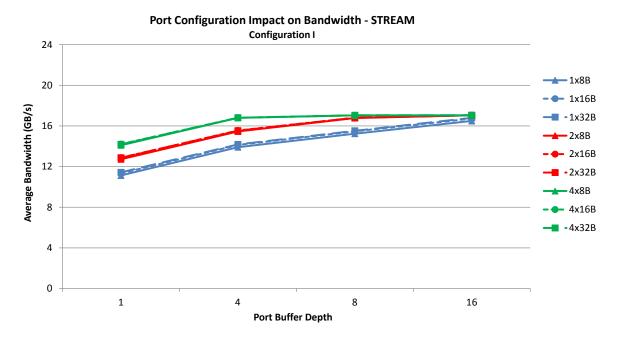

| 79 | Impact of Port Configuration - $STREAM$ (G) | 138 |

| 80 | Impact of Port Configuration - STREAM (I)   | 139 |

# List of Tables

| 1  | Response Packet Transmission Times                                     | 49  |

|----|------------------------------------------------------------------------|-----|

| 2  | Multi-Channel Link Bus Utilization - DDR3-1066                         | 62  |

| 3  | Multi-Channel Link Bus Utilization - DDR3-1333                         | 63  |

| 4  | Multi-Channel Link Bus Utilization - DDR3-1600                         | 64  |

| 5  | Configuration Parameters for Cost-Constrained Systems                  | 74  |

| 6  | MARSSx86 Configuration                                                 | 81  |

| 7  | Normalized Power Consumption of Benchmarks                             | 92  |

| 8  | Bit Field Naming Conventions                                           | 103 |

| 9  | Channel Mapping Schemes                                                | 103 |

| 10 | Channel Mapping - Bandwidth & Execution Time - $facesim$               | 106 |

| 11 | Channel Mapping - Bandwidth & Execution Time - $\mathit{fluidanimate}$ | 107 |

| 12 | Channel Mapping - Bandwidth & Execution Time - $mcol$                  | 108 |

| 13 | Channel Mapping - Bandwidth & Execution Time - $mg$                    | 109 |

| 14 | Channel Mapping - Bandwidth & Execution Time - $stream$                | 110 |

| 15 | DRAM Mapping Schemes                                                   | 112 |

| 16 | DRAM Mapping - Bandwidth & Execution Time - $\mathit{fluidanimate}$    | 115 |

| 17 | DRAM Mapping - Bandwidth & Execution Time - $Sandia\ GUPS$             | 116 |

| 18 | DRAM Mapping - Bandwidth & Execution Time - $mcol$                     | 117 |

| 19 | DRAM Mapping - Bandwidth & Execution Time - $sp$                       | 118 |

| 20 | DRAM Mapping - Bandwidth & Execution Time - $STREAM$                   | 119 |

| 21 | Impact of Return Queue Capacity on Bandwidth                           | 131 |

| 22 | Port Configuration Results - A | 136 |

|----|--------------------------------|-----|

| 23 | Port Configuration Results - D | 137 |

| 24 | Port Configuration Results - G | 138 |

| 25 | Port Configuration Results - I | 139 |

| 26 | Port Buffer Utilization - A    | 143 |

| 27 | Port Buffer Utilization - D    | 144 |

| 28 | Port Buffer Utilization - G    | 145 |

| 29 | Port Buffer Utilization - I    | 146 |

# 1 Background

## 1.1 Introduction

The modern memory system has remained essentially the same for almost 15 years. Decisions made in the past, when the disparity between the CPU and memory clock were not considered to be an issue, are now preventing the memory system from providing the capacity and bandwidth that today's systems and applications demand. Unless modifications are made, the memory system will become an even greater bottleneck than it is now, further impeding performance gains in modern systems.

Unfortunately, alterations to the memory system are met with significant resistance for numerous reasons. First, the fact that the profit margins on memory devices are relatively small (compared to that of a CPU) prevents manufacturers from accepting even modest changes due to the risk of possible failure. Second, any change that is not transparent to the rest of the system also requires support from manufacturers of other system parts. For example, if a new memory module needs to change size or pin-out to support a new feature, this would require cooperation from motherboard manufacturers, CPU and chipset manufacturers, and possibly even operating system and application developers. Lastly, the average consumer is unaware of the importance of the memory system and does not see the benefit when faced with increased costs. In the end, the consumer will typically purchase whatever is cheapest, regardless of the benefit seen by using better products.

To support some level of memory system customization and expandability, commodity DRAM memory is purchased on a PCB, called a dual in-line memory module (DIMM), which uses physical contact (i.e., pins that plug into a motherboard slot) to provide electrical connectivity with the rest of the system. This physical contact is sufficient for electrical signals that operate at low speeds (<100MHz), but as the memory clock has increased to maintain pace with the CPU, this solution is proving to be less than ideal. The signal integrity at these physical contacts is greatly degraded as the memory clock is increased. This issue is exacerbated as more DIMMs are placed in a channel and the further a particular DIMM is located from the memory controller's signal driver [24, 21].

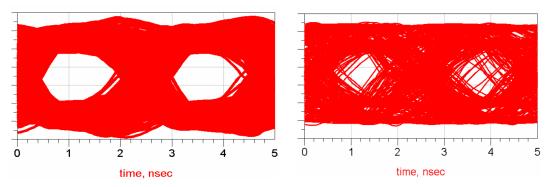

This can be seen in Figure 1 where the signal integrity of the DRAM bus is displayed for a system that has two (Figure 1(a)) and four (Figure 1(b)) DDR2-400 DIMMs. While only two DIMMs are attached to the bus, the data eye is clearly defined. A well defined data eye means that there is a clear differentiation between high and low voltages, and that the signal rise and fall time is short. This makes it easier to interpret what value these signals represent. The data eye is drastically reduced once the DRAM bus has four DIMMs attached, making it more difficult to determine what value is being sent on the bus and increasing the likelihood of errors. The degradation of signal integrity is a result of several factors. The additional DIMMs cause an increase in load seen by the signal drivers, an increase in signal cross-talk, and an increase in signal reflection [40].

(a) Signal integrity seen by two DDR2 DRAM (b) Signal integrity seen by four DDR2 DIMMs DRAM DIMMs

Figure 1: Signal integrity degradation seen on DRAM bus when increasing the number of DIMMs (Original images from [40])

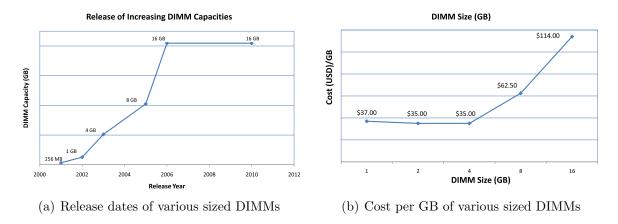

As a result of these issues, when manufacturers increase the memory clock, they must reduce the number of DIMMs allowed in a channel to avoid extraneous costs of mitigating these signal integrity issues. This severely limits the total capacity supported in a system. For example, the original DDR SDRAM standard allowed four DIMMs in a channel, while DDR2 allowed two, and the higher-speed DDR3 variants (i.e., DDR3-1600) only allows a single DIMM of depth [21, 22]. While it is possible to place higher capacity DIMMs in the channel, the overall rate of increase in capacity of a DIMM has slowed due to the difficulties in decreasing the size of a DRAM cell's capacitors. Figure 2(a) shows indirect evidence of this effect as the size of available DIMMs has remained at a 16 GB ceiling for the last five years. Unfortunately, the cost of these high-capacity DIMMs does not scale proportionally with their capacity, as can be seen in Figure 2(b).

Figure 2: Trends In Commodity DRAM

The FB-DIMM memory system was originally introduced to solve the issues outlined above. Each FB-DIMM uses standard DDRx DRAM devices and has additional logic called the advanced memory buffer (AMB). The AMB allows each memory channel to operate on a fast and narrow bus by interpreting a new packetized protocol and issuing DRAM specific commands to the DRAM devices. Unfortunately, the high speed I/O on each AMB resulted in unacceptable levels of heat and power dissipation [24, 7]. The inclusion of the AMB also resulted in more expensive DIMMs relative to similar capacity DDRx DIMMs. These issues ultimately led to the failure of the standard.

To fill the void left by FB-DIMM, vendors such as Intel, AMD, and IBM have devised new architectures to try and resolve the memory capacity and bandwidth issues. Although similar, these new architectures make key changes that prevent the issues that plagued an FB-DIMM system: while each memory channel still operates on a fast, narrow bus, it contains a single logic chip per channel as opposed to one logic chip per module. This allows the new architecture to use of existing low-cost DIMMs,

prevents excessive power and heat in the logic, and reduces variance in latency.

While this buffer-on-board memory system has already been implemented in a small number of high-end servers, the problem exists that each of these implementations differs in non-trivial details. The contribution of the present work is an examination of this new design space to determine optimal use of the resources involved and the exploration of performance enhancing strategies. This includes proper bus configurations for various types of DRAM, necessary queue depths to reach peak DRAM efficiency, and address and channel mappings to ensure an even request spread in order to reduce resource conflicts.

# 1.2 Past, Present and Future Memory Systems

The past five years have seen numerous efforts to devise a next-generation memory system. While many ideas have been proposed, no clear solution has been widely adopted.

#### 1.2.1 Double Data Rate Synchronous DRAM

The most ubiquitous form of memory in use today is the JEDEC standardized double data-rate (DDR) synchronous DRAM. For the past 15 years, this has been the dominant form of commodity memory, eventually breaking into mobile and supercomputing markets due to an overwhelming abundance of parts. The widespread success of DRAM is attributed to the standardization of the device packaging, pin-out, and operating protocol.

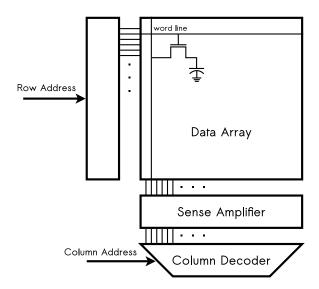

A modern DDR SDRAM device (Figure 3) contains numerous arrays of capac-

itive cells used to store bits of data. Each of these arrays is typically 256Kb each [16, 26]. These arrays are organized into larger banks which operate in parallel and independent of one another; a DDR3 SDRAM device has eight banks [11]. Banks are composed of smaller arrays to prevent extraneous control lines which would span the entire length a row or column resulting in an unnecessary load on the control circuitry.

The data stored in each bank is accessed using separate row and column addresses which are sent to the device using separate commands on different cycles. These commands are sent via the device's command bus in conjunction with a row or column address which are sent via the address bus. The row address is sent to the device first with the ACTIVATE (ACT) command. Upon receiving the ACT command, the entire row of the bank is sent to the sense amplifier. Each bank has its own sense amplifier which is responsible for interpreting the minuscule charge that is stored in a cell's capacitor.

Once this operation has been completed, data may be read out of or into the sense amplifier with a column access command (*READ* or *WRITE*). The amount of time between an ACT and READ or WRITE is dictated by the tRCD (**R**ow to **C**olumn **D**elay) timing constraint.

Figure 3: The modern DDR SDRAM Device architecture

Once the data has finished being read from or written to the sense amplifier, the PRECHARGE (PRE) command is responsible for resetting the sense amplifier and bit lines to prepare for another row access. The amount of time it takes to perform this action is dictated by the tRP (Row Precharge) timing constraint. The point at which this command is issued is dictated by the row buffer management policy. If the PRE command is issued immediately after a column access, then the operation is referred to as a closed page policy. Conversely, if the precharge command is not issued immediately, the sense amplifier retains the row data, which can be advantageous in the case that subsequent requests access this same data. This will mitigate the power and time costs of precharging and re-activating the same row; such a policy is referred to as open page and is used in situations of high address space locality.

Even once the row has been precharged, there are other important timing constraints which must be adhered to before a new row may be activated. For instance the tRC (Row Cycle) constraint dictates the amount of time between subsequent

ACT commands to the same bank. The tFAW (Four Activation Window) is a timing constraint used to restrict the current draw from a particular device by dictating the amount of time in which a maximum of four ACT commands may be issued.

Due to the nature of the capacitors used to store individual bits of data, the representative charge leaks over time, and the intended value dissipates beyond recognition. The *REFRESH* (REF) command resolves this issue by reading a row and placing it back into the data array, thereby refreshing the charge in each cell's capacitor. This is done once every 64 ms. Thus, in a device with 8192 rows, a REF command is typically issued every 7.8 microseconds [28]. The amount of time a refresh operation takes is dictated by the tRFC (ReFresh Command) timing constraint. This specifies the length of time between a REF and another REF or a subsequent ACT command.

Power consumption within a DRAM device comes from several distinct sources:

- Background Power Regardless of the operation currently taking place, there is always a constant dissipation of background energy which is used to operate the control circuitry. This value can vary depending on whether or not a row is currently activated and being held within the sense amplifiers or whether the device is in low power mode.

- Activation and Precharge Power The power to activate and precharge a row within the data array is one of the main sources of power consumption in a DRAM device. As previously stated, when a row is activated, the entire row of the data array is sent to the sense amplifier regardless of how much data is actually needed. At some point subsequent to the activation, the sense amplifier

must be precharged to prepare for a new request. Under heavy utilization, these operations can account for the majority of the power consumed by the DRAM device [18].

- Burst Power This component of a device's power consumptions accounts for each time data is transmitted on the data bus from a read or write request.

The relative size of this component varies with memory system utilization.

- Refresh Power This is the power consumption from refreshing the rows of the DRAM data array. This is normally a constant power draw as the operation is performed at regular periodic intervals.

The ratio of these various sources of power consumption is dependent on how the memory system is being used. An idle memory system's power consumption will be dominated by background power and refresh power. Conversely, in a highly utilized memory system, the activation and precharge power will dominate. The row buffer management policy will also have an impact on the ratio of these sources of power consumption. For example, with an *open page* management policy, it is possible to mitigate some of the activate and precharge power by leaving a row open, therefore causing the read and write burst power to be greater than the activate and precharge power. When all of these sources are accounted for during "high usage" situations of 80% bus utilization, a single DDR SDRAM device consumes approximately 689.5 milliwatts [1], a DDR2 DRAM device consumes approximately 340.1 milliwatts [2], and a DDR3 DRAM device consumes approximately 435.9 milliwatts [4]. These values will vary depending on device capacity, clock rate, and utilization.

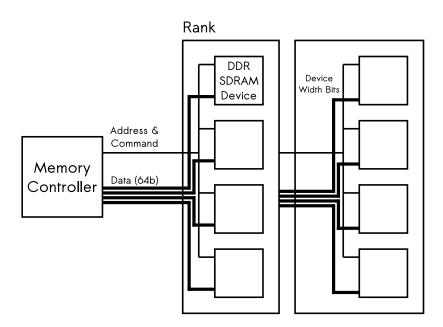

The JEDEC standardized DDR SDRAM device described above is used within the standardized memory system seen in Figure 4. This memory system contains one or more channels composed of a command and address bus and a 64-bit wide data bus. Each of these channels may have one or more ranks of DRAM. A rank of memory is a group of DRAM devices connected in parallel that operate in lockstep by receiving and handling the same requests, at the same time. Each of the device's data buses (which range from 4 to 16 bits) are aggregated together to form the 64-bit data bus. Since DRAM devices do not have a set data bus width, the number of DRAM devices which are used to form a rank can vary. The memory controller, now typically located on the CPU die, is responsible for issuing the DRAM-specific commands detailed above. When reading or writing data out of the device, data is driven on both rising and falling edges of the memory clock, which is where the double data rate nomenclature arises.

Figure 4: JEDEC standardized memory system architecture

As previously mentioned, increasing the clock rate with each successive generation of the DDR standard has limited the number of DIMMs allowed in each memory channel. To circumvent this limitation, most major manufacturers have modified the architecture and widened the memory bus to increase capacity as opposed to relying on additional rank depth. These architectures, called dual- or triple-channel, have two and three DRAM buses, respectively, which can be ganged or unganged.

In a *qanged* architecture, each 64-bit rank receives the same request at the same time as if the DRAM data bus is actually double or triple the size of the rank's data bus. In an unganged configuration, each 64-bit DRAM channel acts independently of the others. While an unganged architecture will allow for greater concurrency and fewer resource conflicts, it requires duplicate logic within the controller to operate each channel independently. Both of these modified architectures do permit higher capacity at the same time as increasing the clock rate, yet the required pin-out (one of the most significant costs to chip manufacturers) on the processor is incredibly high. A modern Intel i7 processor uses over 350 pins for a triple-channel memory system [14]. The current generation (DDR3) can support transfer rates of up to a theoretical 12.8GB/s while operating at 1600Mbit/s [11]. The next generation of DDR SDRAM (DDR4) is expected to be widely available by 2012 [33] yet still faces the same limitations as previous generations and is simply a temporary solution, in that it will still use a wide, multi-drop bus that will still have the speed and capacity issues explained above.

Figure 5: The differences between ganged and unganged ranks or DRAM

## 1.2.2 Registered & Load Reducing DIMM

Another modification to the DDR SDRAM architecture is the introduction of the Registered DIMM (RDIMM) and Load Reducing-DIMM (LR-DIMM) [27] standards. The RDIMM standard was introduced first and alleviated some of the signal integrity issues of high-speed memory modules. These DIMMs use standard DDR3 DRAM devices but place a register between the devices and the main memory controller. This register is responsible for latching all control signals, such as the bank address lines, address bits which address the columns and rows, CAS and RAS signals, and power-down control lines [29]. These modules came at a higher cost; this is due to a lower manufacturing volume relative to unbuffered DIMMs and not due to higher part costs, which comprise a simple buffer. A major benefit to this modification is that it

maintains both the interface and protocol of the existing standard, thereby allowing consumers and system manufacturers to retain old hardware while still having the benefit of the increased performance provided by these new DIMMs.

Similar to the RDIMM standard which buffers the control and address signals, an LR-DIMM places a memory buffer (MB) [30] on all of the signals between the CPU and DRAM (Figure 6). This includes the entire data bus and data strobe lines, along with the control and address lines. This provides an even greater boost in signal integrity and reduction in load on the main controller relative to an RDIMM because there is now only a single load per DIMM as opposed to a load equal to the number of DRAM devices. Again, this allows a faster memory clock with an even greater number of DIMMs possible in a single channel. This is aided even further by the inclusion of a phase-lock loop circuit which re-drives the clock signal, allowing it to be run at a higher frequency without fear of noise or signal degradation.

As with RDIMMs, these modifications have no impact on the existing interface or protocol, making the LR-DIMM attractive to both the memory manufacturers who are wary of costly modifications and to the consumers and vendors who are not required to make modifications to existing systems. The only noticeable difference seen to the system is a one cycle increase in latency to account for the latching of signals and data before it is sent to the DRAM device or memory controller. While this modification will extend the life of the DDR SDRAM architecture, it is still a temporary fix to the underlying issues facing modern memory systems. LR-DIMMs with a capacity of 16GB and 32GB are expected to be released to market at some point in 2011.

Figure 6: The LR-DIMM architecture

### 1.2.3 Fully Buffered DIMM

In 2004, an entirely new memory architecture standard was adopted that was intended to alleviate the problems with the current design. The new design, called fully buffered DIMM (FB–DIMM), uses the same DRAM devices as DDR2 and DDR3 SDRAM DIMMs, but operates on a faster and more narrow bus relative to the standard DDR architecture [6]. This was made possible by the inclusion of a small controller on each DIMM called the *advanced memory buffer* (AMB) [10]. The AMB is responsible for interpreting the packetized protocol and controlling the DRAM devices located on each DIMM. The standard defines a point-to-point interface between DIMMs, which causes the memory system to appear as a multi-hop store & forward network [22]. This architecture allows a much higher capacity (up to 768 GB per system) and significantly higher bandwidth per pin due to its increased clock.

An FB-DIMM memory channel operates on two separate logical buses: the north-bound channel and the southbound channel [24, 22]. These channels are different widths to account for the disparity between reads and writes during typical operation; the northbound channel (going toward the CPU) is 14 data lanes and the southbound channel (going away from the CPU) is 10 data lanes [9] (Figure 7). The resulting peak bandwidth achievable by each bus is dependent on the DRAM devices used on the module. A multiple of the DRAM reference clock is used as the frequency for the northbound and southbound bus and results in the ability to transfer twice as many reads as writes [23]. For example, when an FB-DIMM uses DDR2-667 devices, the channel can support peak bandwidth of 8 GB/s.

To account for such narrow buses, requests and responses are encapsulated in packets or *frames*. As these frames are transmitted on their respective channel, the AMB interprets the contents to determine proper routing or to generate standard DRAM commands for local DRAM devices. To accommodate proper packet transmission, each of these channels operates at speed exactly six times that of the DRAM devices which populate the DIMM (i.e., DDR3-1333 with a 667MHz clock rate operates on FB-DIMM channels of 4GHz).

Figure 7: The FB-DIMM memory system

A southbound frame consists of up to three independent commands or a single command and 72 bits of write data (64 data bits and 8 ECC bits). In a frame made up of three separate commands, each command is destined for a different DIMM within the channel. These commands can either be a typical read or write requests (which are then interpreted by the AMB into standard DRAM commands like ACT, READ, WRITE, or REFRESH) or channel commands which are used to manage operating conditions within the FB–DIMM channel [24]. These commands include debug operations, channel syncing operations, reset commands, and control register setting commands. Scheduling at the DRAM level is still handled by the main memory controller with the AMB simply interpreting the frames it receives into DRAM based commands.

A northbound frame consists of 144 data bits retrieved from the DRAM as a result of a previous request (128 data bits and 16 ECC bits). The 128 data bits corresponds to the data retrieved from a single DRAM device cycle where 64 bits are transmitted

on each clock edge.

Unfortunately, an unforeseen consequence of the FB-DIMM architecture's pointto-point nature and the use of high speed I/O in each AMB caused unacceptable

levels of heat and power dissipation. Under heavy load, a fully populated FB-DIMM

channel of 8 DIMMs (totally 32 GB) requires over 90 watts while under moderate load

[8, 3], which is on par with CPUs at the time. Tests have shown that an FB-DIMM

system consumes over 800% more power than a comparable DDR2 memory system

[17]. Because of this issue, adoption of the standard slowed, and FB-DIMM was

eventually removed from all major technology roadmaps. While no clear successor to

FB-DIMM has been proposed, major vendors have taken it upon themselves to find

solutions to the capacity and bandwidth issues. They have done this by designing

new architectures which, like FB-DIMM, use existing DRAM devices attached to

intermediate logic, operating on a relatively narrow, high-speed bus. These new

architectures are simply organized in a different fashion.

#### 1.2.4 IBM Power 7

IBM's new 8-core Power7 processors (**Figure 8**) have implemented a novel memory system which increases DRAM capacity to up to 256 GB per CPU socket (and up to 8 TB in a system using a Power795 processor) with an access rate of 1066MHz [12]. All Power7 CPUs have two on-die memory controllers each with 8 KBytes of scheduling window [25]. The memory controller communicates with 4 logically independent channels, for a total of 8 memory channels per CPU socket. Unlike a standard DDR3 memory system, a channel is now two logically separate, uni-directional buses which

are faster and more narrow than the standard DRAM bus. Like FB-DIMM, this is possible through the utilization of an *advanced buffer chip* which is placed between the CPU and DIMMs.

Each of the advanced buffer chips communicates with the on-die memory controller via a 6.4 GHz channel which has 8 data lanes towards the DIMM and 16 data lanes towards the CPU. With 8 of these channels, a CPU has a total of 136.44 GB/s of available memory bandwidth [12]. Unlike the FB-DIMM standard where an AMB is responsible for communicating with other AMBs in a channel, the advanced buffer chip used in the Power7 memory architecture is only responsible for communicating with a single DIMM. This alleviates some of the issues with the FB-DIMM design, such as excessive power dissipation within the AMB due to constantly communicating with other DIMMs in the channel and variable latencies caused by a multi-hop store & forward network. The design of the advanced buffer chip is propriety to IBM [25] so the protocol used to communicate with the CPU is unavailable. Due to the widths and operating frequency of each channel, it would be impossible to use the FB-DIMM protocol.

Figure 8: IBM's Power7 memory architecture

### 1.2.5 Intel Scalable Memory Interface

After it was clear that FB-DIMM had failed, Intel decided to modify the architecture slightly to alleviate the issues with the design instead of abandoning it completely. At one point called FB-DIMM2 [15], Intel's Scalable Memory Interface (SMI) is a memory system architecture for Nehalem EX processors and has recently been implemented into IBM's System X and BladeCenter systems [37]. The block diagram for this system can be seen in **Figure 9**. Similar to both the Power7 memory system and FB-DIMM, this design is made possible by a logic chip attached to each channel. The logic chip used in this system is called the Scalable Memory Buffer (SMB) and is placed between standard DDR3 RDIMMs and the CPU that it communicates with over the SMI buses.

The SMI interface between the Nehalem-EX processor and SMB consists of two uni-directional buses with 9 southbound data lanes (+1 for CRC) for requests and 12 northbound data lanes (+1 for CRC) for responses. The rate at which these buses are operated is dependent on the CPU currently in the socket and includes 4.8 Gb/s,

5.86 Gb/s, or 6.4 Gb/s [13]. The SMB is also responsible for operating two logically independent, JEDEC standardized channels of DDR3 RDIMMs where each channel is allowed up to two DDR3 RDIMMs. Each Nehalem-EX processor has four SMIs, thereby providing a total capacity of up to 256 GB per CPU socket and a total memory channel bandwidth of 67.2 GB/s when clocked at 6.4 Gb/s.

As with IBM's Power7 systems, Intel's architecture is differentiated from the FB-DIMM standard by using the SMB to only communicate with the DIMMs as opposed to other logic. This alleviates many of the issues with the FB-DIMM design such as unacceptable heat and power dissipation and variance in latency. Again, similar to the Power7 memory architecture, the SMI and SMB are both propriety, and therefore the communication which occurs over each SMI bus to the SMB is unknown. A protocol similar to FB-DIMM is likely since Intel developed the original standard, yet they specifically state that the original FB-DIMM protocol is not supported within an SMI/SMB system [13].

Figure 9: Intel's Xeon 7500 memory architecture

### 1.2.6 AMD G3 Memory Extender

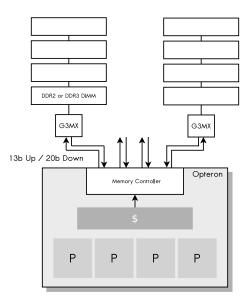

AMD had also proposed a similar solution to the issues facing current memory system design. Just like IBM and Intel, they proposed placing a piece of logic called the Socket G3 Memory Extender (G3MX) between an Opteron CPU and either DDR3 UDIMMs or RDIMMs. Each Opteron CPU would have an on-die memory controller communicating with four G3MX devices over separate channels. Each of these channels are made up of two logically separate and uni-directional buses with a request bus of 13 data lanes and a response bus of 20 data lanes (Figure 10). This leads to a memory channel which only uses 66 pins (when differentially signaled), far less than the previous Opteron DDR memory channel. Therefore, with the same number of pins as a DDR memory channel, the system's memory capacity could be more than doubled.

The G3MX would be responsible for controlling up to 4 standard DDR3 U/RDIMMs giving each processor a total of up to 16 DIMMs per socket (as opposed to the 8 DIMM limitation of previous Opteron based systems). The architecture is similar to IBM and Intel's architectures detailed above; it places logic between the CPU and DIMMs, and communicates over fast and narrow buses of unequal widths. The only discrepancies between all three of these designs are the widths of the respective request and response buses and the amount of DRAM allowed on the far side (relative to the CPU) of the logic. AMD officially canceled the G3MX memory system in 2008, and they have yet to announce a replacement [35].

Figure 10: AMD's G3MX memory architecture

# 2 Buffer-On-Board Memory System

It is clear that with Intel's SMB/SMI systems, AMD's G3MX, IBM's Power7, and even JEDEC's LR-DIMM, near-term memory system design is heading in a similar direction: numerous concurrent channels of DRAM which have logic (either a controller or buffer) located between the DIMMs and the CPU, with communication provided over a narrow and fast bus. The architecture solves all the issues facing commodity memory system design today - it increases capacity, increases aggregate bandwidth, increases speed, and allows for far greater concurrency without increasing pin count. These benefits are a result of the introduced logic which improves signal integrity when faced with physical contact based electrical connections and reduces the required CPU pin-out to the memory system, allowing operation at a higher frequency.

This architecture also alleviates many of the issues that plagued the FB-DIMM memory system. The excessive heat and power dissipation that resulted from communication between chained AMBs is no longer an issue as this new design only utilizes the intermediate logic to communicate with the CPU and DIMMs. There is no longer an issue with large variance in request latency which resulted from chained AMBs and FB-DIMM channels containing a large number of DIMMs. Lastly, the high costs involved with FB-DIMMs can be circumvented as the logic can now placed on the motherboard, allowing standard DIMMs to be used instead.

While a number of influential vendors are currently working on the concept, few systems have actually been implemented, and those which have, all vary in their specifics, such as bus speed and width or rank depth. Therefore, while the architecture is still young, an examination of the design space is necessary.

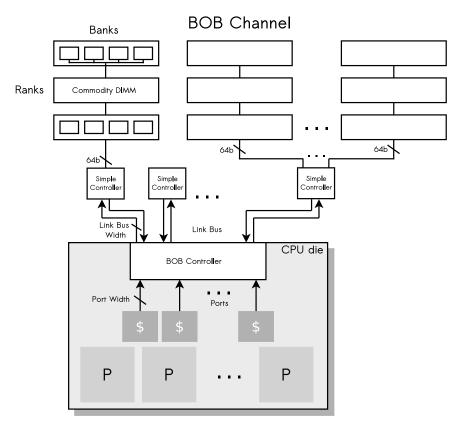

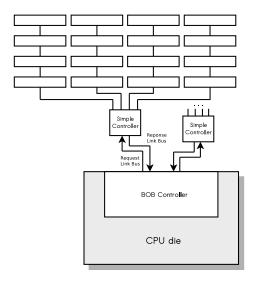

### 2.1 Architecture Overview

The generalized form of this buffer-on-board (BOB) memory system architecture can be seen in Figure 11. It consists of DRAM channels populated with commodity DIMMs which are composed of standard DDR devices. These DIMMs can be unbuffered, registered, or even load-reducing DIMMs. Each of these BOB channels could be considered identical to a regular, JEDEC-standardized memory system. The control and data bus, operating protocol, and timing constraints are the same ones used in a normal memory system. The simple controller in each BOB channel operates as the intermediate logic located between the DIMMs and the main, on-die memory controller.

Each simple controller is responsible for controlling the DRAM, as well as receiving requests and returning data back to the main memory controller (as opposed to the DRAM talking directly to the main memory controller). Communication between the simple controller and the CPU occurs over a *link bus* which is narrower and faster than the DRAM bus which communicates with the DIMMs. Unlike the DRAM bus, which has separate control and data signals, the lanes which comprise a link bus are for general purpose communication. The link bus is full-duplex where the request (towards the DRAM) and response (towards the CPU) data lanes may be different widths and operate at some speed faster than the DRAM.

Figure 11: The BOB memory system architecture

The BOB architecture has an interesting characteristic of having three separate clock domains - the CPU clock (which also corresponds to the main BOB controller clock), the link bus clock between the BOB controller and simple controller, and the DRAM clock between the simple controller and the DIMMs it controls. The DRAM clock is defined by the type of DIMM which populates a channel (i.e., if DDR3-1066 DIMMs are used, then the DRAM clock is 533MHz). The link bus clock needs to be faster than the DRAM clock to account for the narrower bus. Obviously, the CPU clock is determined by the CPU. The ratio of each of these clock rates is an important factor in the behavior of each portion of the BOB memory system. Such an architecture provides a chance to optimize in multiple dimensions. Depending

on a system's purpose, the optimal organization of a BOB memory system might vary. Only through an accurate and detailed model and precise simulation can these optimizations be determined.

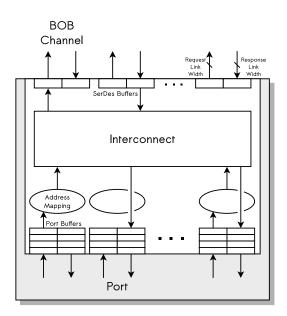

### 2.2 Main BOB Controller

The main BOB controller (Figure 12) that resides on the CPU die is an essential aspect of the architecture. The BOB controller is responsible for the typical functions of a commodity memory controller, such as address mapping and returning data to the cache. The address mapping that takes place within the BOB controller uses the address of a request to determine which BOB channel should receive said request. Like the address mapping in a commodity system, a particular portion of the bits which make up the address are used to determine this mapping.

Communication with the cache and CPU is executed over the main BOB controller's ports, which are logically separate, full-duplex lanes. Each port has a corresponding input and output buffer which store requests and responses while awaiting arbitration. The width of each port is on the order of magnitude similar to that of the data bus used to operate the cache. The speed of each port is dictated by the frequency of the CPU. A cross-bar switch is used to route requests and responses to and from port buffers to ensure that a request from any port is capable of being sent to any link bus. The width of this cross-bar switch is the same as each port to ensure an unimpeded flow of requests and data.

Unlike a commodity memory controller, the BOB controller is also responsible for

packetizing requests and interpreting response packets sent to and from the simple controllers over the narrow link bus. Since the link bus is narrower than the DRAM bus, requests and responses must be encapsulated within a packet. These packets are then sent over the link bus during multiple clock cycles. This is accomplished with a serialize-deserialize (SerDes) interface and associated buffer for the request and response path of each link bus. These buffers are written into by either the crossbar switch when issuing requests or the response link bus when returning a response packet. Items are removed from the SerDes buffers when the destination port is free and there is room in that port's buffer, while ensuring that a request is returned to the same port which it was received. When removing items from a SerDes buffer to send via its respective port, a round-robin scheme is used to ensure starvation does not occur.

Figure 12: The main BOB controller's block diagram

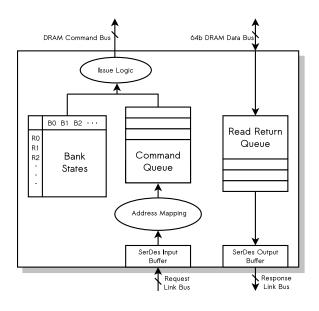

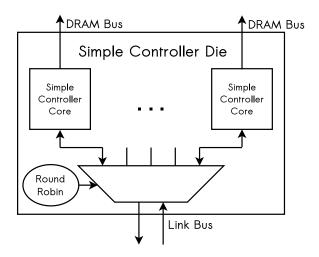

# 2.3 Simple Controller

The added logic placed between the main BOB controller and the JEDEC compliant DRAM channels is referred to as the *simple controller* (Figure 13). The simple controller has two main functions: controlling the DIMMs using the standard DRAM interface and sending and receiving request and response packets back to the main BOB controller over the request and response link buses, respectively. Upon receiving a request packet, the simple controller must translate the packet into a series of DRAM specific commands such as ACTIVATE, READ, or WRITE. This process also involves address mapping similar to that which takes place in a commodity memory system by a normal memory controller. Particular portions of the address in a request are used to determine the rank, bank, row, and column that will service this request. The address of each resource is then paired with the appropriate command (i.e., row address with ACTIVATE, column address with READ or WRITE, etc.).

Once the address has been mapped to the appropriate resources, and the correct DRAM commands have been created, they are placed in the simple controller's command queue. The command queue is searched out of order to find any possible command which may be issued while still respecting all timing constraints imposed by the DRAM devices. The simple controller is also responsible for keeping track of and issuing REFRESH commands to the DRAM, in order to prevent data loss from capacitive leakage.

Upon the completion of a READ's data burst from the DRAM to the simple controller, the data must be stored within the simple controller while it is packetized and returned to the main BOB controller. This data is stored in the read return queue. This is an essential new portion of the architecture and was not necessary in a commodity memory controller. It allows the operation of the DRAM to continue while data is being returned to the main BOB controller on the response link bus. If this queue is full, commands can not be issued to the DRAM. If data were to be returned to the simple controller from the DRAM when there is no space in the queue, the data would be lost. With no assurance as to the point in the future when space will be available in the queue, the DRAM must be immediately stalled until space is available.

Figure 13: Simple controller block diagram

Similar to a commodity memory controller, the simple controller is responsible for the row buffer management policy. This policy dictates at which point a row of the DRAM should be precharged following a column access. In a BOB memory system, the simple controller uses a closed-page row buffer management policy. With this policy, a PRECHARGE command is issued to the DRAM as soon as possible (while still adhering to timing constraints) following a column access (either a READ or WRITE). A closed-page policy is used for three important reasons.

First, the closed-page policy favors systems with large processor counts such as servers which typically use this policy by default. With a large number of processors executing numerous threads concurrently, the intermingling of request streams issued to the memory system will tend to negate any address space locality [24]. Therefore, the likelihood of having subsequent column accesses to the same row is greatly reduced making an *open page* policy ineffective. Since the BOB memory system is targeted at server-based systems, the same principles apply.

Secondly, one of the main benefits of the implementation of a BOB memory system is the increased concurrency available within the memory. This reduces the likelihood of a resource conflict. At the same time, using a greater number of logically independent DRAM channels will reduce the likelihood of subsequent requests being mapped to the same row, thus reducing the overall effectiveness of an *open page* policy even further.

Lastly, the logic required to implement an open page row buffer management policy is significantly more complex than a closed-page policy. A greater amount of state is necessary to ensure adherence to all timing constraints, and various heuristics are required to prevent request starvation and refresh timing violations. This would therefore make the simple controller more expensive to implement and require a greater amount of power to operate. One of the main reasons FB-DIMM failed was because the introduced logic (AMB), which facilitated the use of narrow buses, also required excessive power and generated excessive heat. Increasing the complexity and

power consumption of the simple controller could result in similar issues in a BOB memory system.

### 2.4 Packets

Due to the relatively narrow width of each link bus used within the BOB memory system, a packetized interface is required between the main BOB controller on the CPU and each simple controller. Two types of packets are used: a request packet and a response packet. Each packet is sent on the corresponding link bus (i.e., request packets are sent on the request link bus and response packets are sent on the response link bus) over multiple clock cycles. The format and total size of these packets is important for the generalized model as it determines the amount of time it takes a request or response packet to traverse each link bus. The format for these packets can be seen in Figure 14. While certain fields within the packet might not be fully utilized, it is important that the total size of the packet be some even factor of its respective link bus's width to ensure that link bus cycles are not wasted sending only a portion of the packet.

Figure 14: BOB packet definition

A request packet being sent on the request link bus must contain the request's address, the request type, and the data if said packet is a write request. The type of request can either be a read or write. The amount of data included in a write

request packet is always 64 bytes since the DRAM attached to each simple controller are commodity devices which expect that amount of data. When a write request is received, this data is stored in a queue while awaiting the WRITE command to be issued to a particular rank of DRAM.

A response packet will contain data requested by a READ command as well as the address of the initial request for identification purposes. This is necessary due to out-of-order issuing of requests both within the BOB controller and simple controller, and may be completed at different times. The order of requests to the same address is always maintained.

# 3 BOB Simulation Suite

To properly evaluate this new architecture, a simulation suite is developed with a strong focus on hardware verification and comprehensive, detailed system modeling. Two separate simulators are used in this suite: a BOB memory system simulator developed at the University of Maryland, and MARSSx86 [31], a multi-core x86 simulator developed at SUNY-Binghamton. Together, they create an accurate model of a processor which boots an operating system, launches an application, and interacts with the cache and memory system.

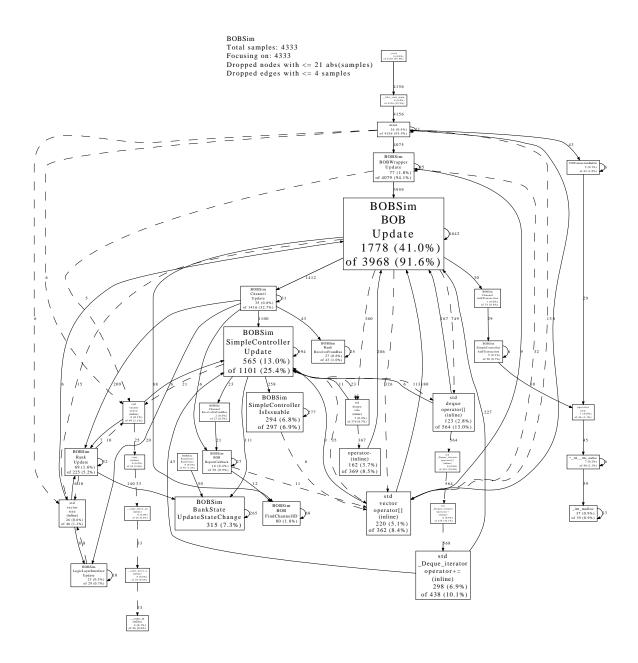

### 3.1 Simulation Framework

The BOB memory system model is a cycle-based simulator written in C++ that encapsulates the main BOB controller, each BOB channel, and their associated link bus and simple controller. Each of the major logical portions of the design have a corresponding software object and associated parameters that give total control over all aspects of the system's configuration and behavior. Some simple examples include the type of DIMMs and number of ranks within an individual BOB channel, the total number of BOB channels, or speed and width of each link bus. The BOB simulator may be run in one of two modes – a stand-alone mode where requests from a parameterizable, random address generator are issued directly to the memory system or a full-system simulation mode where the BOB simulator receives requests from MARSSx86. A google-perftools analysis and call-graph can be seen in **Appendix A**. Simulating a BOB memory system in stand-alone mode may provide many insights

into a system's behavior, yet a full-system simulation is the most ideal situation as it will show important interactions and behaviors which might not have been obvious otherwise. In order to perform a full system simulation, an accurate CPU and cache simulator must be selected and integrated. After considering several CPU simulators, MARSSx86 is selected. MARSSx86 merges the highly detailed, out-of-order x86 pipeline models from PTLSim [41] with the QEMU emulator. MARSSx86 augments the original PTLSim models with multi-core simulation capability and a configurable coherent cache hierarchy.

The ability to simulate multi-core environments is critical since multithreaded workloads are quickly becoming the rule rather than the exception. Additionally, it is difficult to imagine a single threaded application being able to take full advantage of the tremendous bandwidth provided by a BOB memory system. MARSSx86 provides a full system simulation capabilities that allow the simulator to capture the effects of the cache, virtual memory, and kernel interaction. These things are key factors in the efficient operation of the memory system. The CPU models are highly configurable, and it is possible to change the internals of the CPU or behavior of caches to take advantage of new features (for example, replacing a traditional memory bus with a number of ports).

To attach the BOB memory system model to the MARSSx86 simulator, the memory controller class in MARSSx86 is modified to reroute requests and responses. As requests arrive at the memory controller within MARSSx86, they are sent to the main BOB controller's ports. The heuristic for assigning requests to specific ports can be altered – for example, requests could round robin over all ports, or a specific

set of cores might always use a specific port. The implications of this concept is fully explored in the full-system simulation section (4.2). If there are no available ports, or all port buffers are full, the CPU will be stalled until requests can be issued.

The MARSSx86 memory hierarchy contains a clock signal which is used to drive the clock of the BOB simulator. Since a BOB memory system contains multiple clock domains, the clock provided by the MARSSx86 simulator is multiplied or divided to create the correct frequency for each portion of the architecture. Once a memory request is complete and finished being sent out of the main BOB controller's port, the data is returned to the MARSSx86 memory controller using a callback function. The memory controller then sends the completed requests back up the cache hierarchy to the CPU.

Just as in a real CPU, thread execution is stalled while waiting for a memory request to complete. This interaction between the CPU and memory system is key because it shows the impact of an optimally configured memory system and the impact the memory system can have on a program's execution. DRAMSim2 uses a similar method to connect to MARSSx86 [32], which makes it easy to run the same workloads in both simulators to compare the system level benefits of a BOB memory system over a traditional DDR2/3 memory system.

### 3.2 Hardware Verification

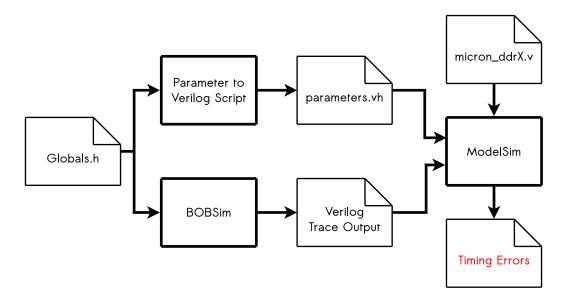

An important aspect of this simulation framework is its ability to validate simulated behavior against that of actual hardware. Since the DIMMs used in a BOB memory system utilize the same DRAM devices, same interface, and same timing constraints as those in a commodity system, validating this portion of the simulator can be achieved in a manner similar to that of DRAMSim2 [32]. Micron Technology publicly provides Verilog HDL models for each of the DRAM devices that it produces. These models determine whether or not a timing constraint has been violated based on a series of inputs from a hardware behavioral simulator like ModelSim. Therefore, with simple Python scripts to massage simulator output, the validity of the simulation can be confirmed.

Figure 15: The verification process using ModelSIM

During a BOB memory system simulation, each DRAM channel produces a bus trace file consisting of a command (i.e., ACTIVATE, READ, WRITE, PRE) or data and the cycle on which it was issued. This file is post-processed by a separate Python script that generates a series of Verilog compatible commands. These Verilog commands are used in conjunction with ModelSim and the Micron HDL models to ensure the timing of both commands and data issued on the bus are cycle accurate at the

DRAM level. The parameters used in each simulation are parsed out of the global BOBSim header file (which defines all parameters in a simulation) and are placed in a Verilog header file that tells ModelSIM specifics about the device it is simulating. A block diagram of this process can be seen in **Figure 15**. The BOB simulator uses timing and device parameters from a Micron DDR3-1066 device (MT41J512M4-187E), a DDR3-1333 device (MT41J1G4-15E), and a DDR3-1600 device (MT41J256M4-125E), yet any JEDEC standard device will work.

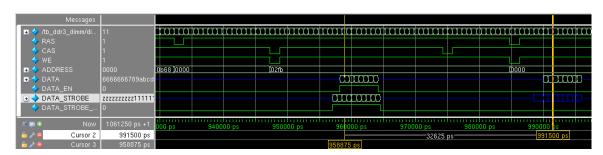

The specific signals which are used in this verification are the signals which make up the command bus (RAS, CAS, WE), the address bus (for bank, row and column), and the data bus. For all simulations, the first one million DRAM cycles are verified with the above technique; all are always successful. While the overall purpose of utilizing ModelSIM's behavioral modeling abilities is to ensure timing constraints are not violated within BOBSim, it also provides the ability to visualize the operation of the DRAM. In **Figure 16**, a read and write are issued and the corresponding signals are shown accordingly.

Figure 16: A read and write cycle shown in ModelSIM

## 4 Simulation Results

When evaluating the characteristics and behavior of this new architecture, we performed two experiments: a limit-case simulation where a random address stream is issued into a BOB memory system as fast as possible and a full system simulation where an operating system is booted on an x86 processor and applications are executed. The limit-case study is useful for identifying the achievable maximum sustained bandwidth and the behavior of the system in extreme situations. Many server and HPC applications generate address streams that have little locality (temporal or spatial) and appear random. In contrast, a full system simulation gives a much more realistic picture of the new memory system's interaction with the cache and processor, operating system, and actual applications.

A host of benchmarks are selected with an emphasis on multi-threaded workloads to demonstrate the types of request streams the BOB memory system is likely to encounter. It is necessary to have a wide variety of benchmarks because variations in the memory request stream cause vastly different behaviors and subsequent performance. The list of benchmarks is:

- The PARSEC benchmark suite is a set of multi-threaded benchmarks designed by Princeton aimed at testing shared-memory CMPs. The memory intensive benchmarks of the suite include *fluidanimate*, *facesim*, and *bodytrack*.

- The STREAM benchmark is a memory bandwidth test designed to demonstrate real world achievable performance via software. This benchmark is run for 10 iterations and uses a two million element array.

- GUPS (Giga-Updates Per Second) is a benchmark designed to mimic the computational and memory behavior of sparse matrix updates, graph traversals, and cryptographic algorithms. This benchmark performs 256M updates on a 1GB array with a 64-byte element size.

- Sandia National Lab's implementation of GUPS. This benchmark uses a 4GB array size and performs 2 million updates.

- The NAS parallel benchmark suite is a set of fluid dynamics computations released by NASA.

- MCOL is a benchmark which scans over a matrix in memory. It uses eight threads to perform 25 iterations over a 64MB array.

When considering the cost of a particular system's implementation, design tradeoffs that are considered include total pin count required by the CPU, power dissipation of both DIMMs and simple controllers, and the physical space required (or total DIMM count).

### 4.1 Limit-Case Simulations

For the limit-case simulations, the BOB simulator is run in a stand-alone mode where memory transactions are added directly to the BOB controller via an execution wrapper. This wrapper is also responsible for collecting and analyzing useful statistics. The generated request stream can be tailored to issue at a specific frequency or readwrite ratio. For these simulations, requests are issued as soon as possible with a mix

of 2/3 reads and 1/3 writes.

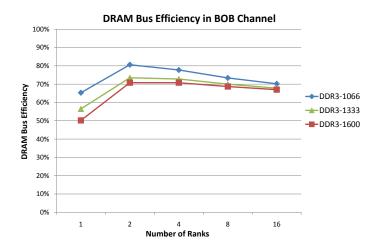

### 4.1.1 Simple Controller & DRAM Efficiency

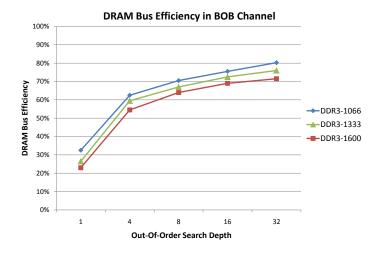

Commodity memory system design has been examined and analyzed extensively [20, 24, 39, 19]. Because each BOB channel uses commodity DIMMs, operates on the same data and command buses, and requires the same operating protocol and timing constraints, it stands to reason that the previous insights, optimizations and analysis targeting commodity systems should apply here as well. When observing an individual BOB channel's behavior, the simulations confirm and reinforce these previous insights. For example, the impact of an increasing number of ranks of DDR3-1066, DDR3-1333, and DDR3-1600 on the DRAM bus efficiency can be seen in Figure 17. Efficiency begins to drop after two and four ranks due to the increased necessity of idling the data bus for arbitration when switching between the ranks. While the use of 8 and 16 ranks of DRAM is uncommon due to electrical constraints, this shows that even the logical behavior of the system displays a decrease in performance when faced with an increasing number of ranks. The peak efficiency achieved is also verified by manufacturers results [5] and prior research [36].

Figure 17: Increasing number of ranks in memory system has a negative impact on DRAM bus efficiency

In a similar vein, the simple controller in each BOB channel is comparable to a typical memory controller in a standard memory system. Therefore, characteristics and optimizations which have been previously identified in commodity memory controllers should apply here as well. Parameters such as address mapping and queue depths have shown to have a significant impact on performance [39], which is also the case in BOB systems. Increasing the out-of-order depth and command queue size allows the simple controller to more easily find commands to issue (while still adhering to the timing constraints), thereby increasing the DRAM bus efficiency (**Figure 18**). The increased queue depth and search facility will increase costs such as die size and power consumption. Therefore, an appropriate out-of-order queue depth can be determined either by the required performance or outside constraints, such as target power consumption or transistor count. Given this, there are still diminishing returns after a depth of eight; doubling the queue to 16 only increases DRAM efficiency by approximately 5% in all cases.

Changing some parameters within the simple controller will have no impact on the performance during a limit-case simulation due to the random nature of the address stream. Parameters such as the address mapping scheme, which normally have a significant impact on performance, will not have any effect due to the equal likeliness of all bit combinations within the address. Other parameters, such as the return queue depth will have different behaviors under the limit-case compared to that of a full-system simulation, since the random address stream ensures an equal spread of requests both spatially and temporally. These parameters are explored further when simulations are run in full system mode with MARSSx86.

Figure 18: Increasing the out-of-order search depth increases DRAM bus efficiency

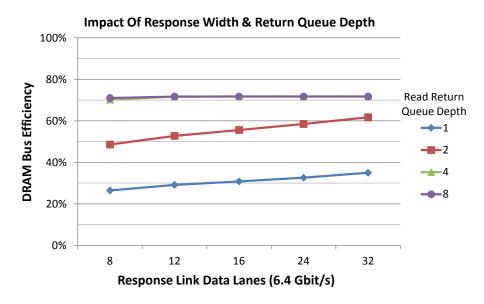

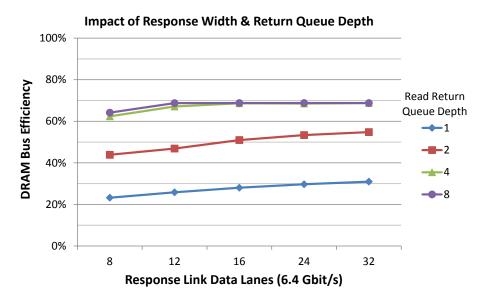

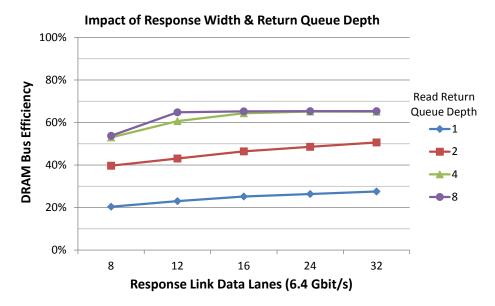

The simple controller must also have features that differentiate it from a commodity memory controller as a result of serializing communication on the link bus. The read return queue within each simple controller is responsible for storing requested data before it is packetized and transferred out on the response link bus back to the main BOB controller. If this queue is full, no further read or write commands will be issued to the DRAM until there is space within this queue. While write commands

do not require space in this queue, they are still stalled to maintain proper request ordering. It is possible to continue issuing ACT commands to prepare rows for access, although this will increase background power consumption since rows will be left open for a longer amount of time (within limit-case simulations, the ACT commands are continually issued when possible).

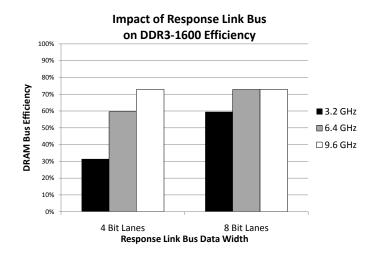

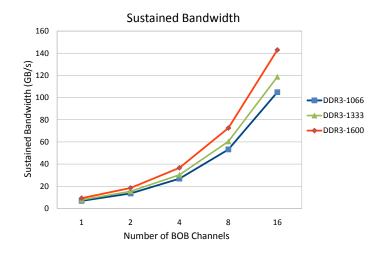

The rate at which items are removed from this queue is determined by both the width and speed of the response link bus. A parameter sweep is performed on both the depth of the read return queue and the configuration of the response link bus to detail the impact these decisions have on the achievable efficiency of different speeds of DRAM. The results can be seen in can be seen in **Figures 19, 20, & 21**.

The efficiency of all DRAM speeds is greatly impeded when the read return queue only provides storage capacity for a single response. To prevent overflowing the queue, space in the queue is reserved for the incoming data upon issuing the READ command to the DRAM. Therefore, when the queue depth is one, all subsequent requests are stalled, not only while the response is being sent over the response link bus, but while the data is being retrieved from the DRAM as well. Therefore, as soon as a single READ command is issued, all requests are stalled until the data has been retrieved from the DRAM and it has finished being sent back to the main BOB controller. This situation is entirely too restrictive and performance can be more than doubled by simply having a queue depth of two.

Figure 19: Response link and return queue depth impact on DDR3-1066 DRAM bus efficiency

Figure 20: Response link and return queue depth impact on DDR3-1333 DRAM bus efficiency

Figure 21: Response link and return queue depth impact on DDR3-1600 DRAM bus efficiency

With a queue depth of two and four, the efficiency is significantly increased. The increase in storage capacity allows a better utilization of the parallelism available within modern DRAM devices. As the response link bus is widened, response packets are removed more quickly thereby clearing room in the queue for subsequent requests. With a depth of four, the DRAM is rarely stalled as a result of the read return queue reaching maximum capacity. The gains seen by increasing the response link bus width eventually taper off as the DRAM has already achieved maximum attainable efficiency.

In Figures 19, 20, & 21, the link bus is clocked at 3.2 GHz and utilizes double data rate transferring of packets (6.4 Gbit/s). If the link bus clock is increased, the width of the bus becomes less of a determining factor in the efficiency of the DRAM. When the link bus is clocked at 6.4 GHz (12.8 Gbit/s), 8 data lanes is already sufficient to reach peak efficiency (Figure 22). While a 9.6 GHz link bus might not be feasible

now, if future technology enables this to be possible, the width of the link buses can be reduced even further without any negative impact on performance. This would greatly save on CPU pin-out costs, an important factor in chip fabrication.

Figure 22: Response link bus configuration's impact on DRAM efficiency

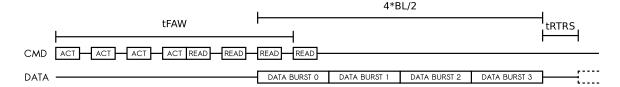

It is possible to use parameters and behaviors of other parts of the system to help quantify decisions about the read return queue and response link bus. The DRAM timing parameter tFAW was introduced to prevent large current draw while performing numerous concurrent row-activation operations. The timing parameter dictates a sliding-window of time in which at most four ACTIVATE commands may be issued. Indirectly, this also determines the longest possible period of uninterrupted data being retrieved from the data bus (Figure 23). This situation can be used as a lower bound for the read return queue capacity. Evidence of this can be seen in Figures 19, 20, & 21. When the queue depth is four, the system is capable of reaching peak efficiency once the response link bus bandwidth is capable of removing the four requests fast enough. This is not the case for more shallow queue depths.

From the DRAM perspective, this is the worst case scenario for the read return queue but will be explored in the context of the whole system in later sections.

Figure 23: The impact of tFAW on the DRAM operation and the longest period of uninterrupted data retrieval

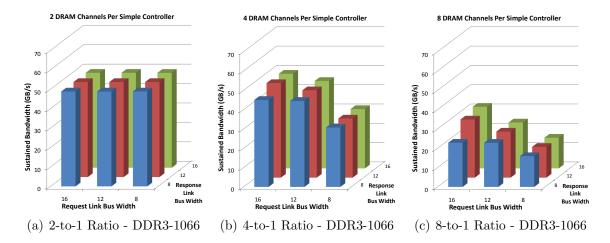

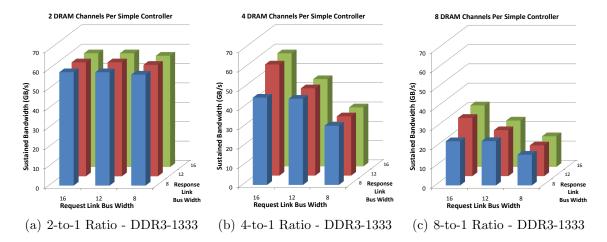

### 4.1.2 Link Bus Configuration

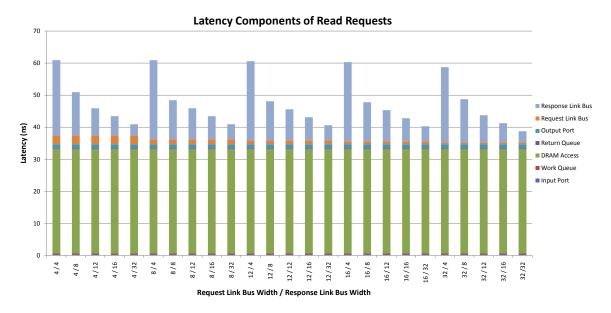

The overall performance of a BOB memory system is inherently linked with the efficiency of each DRAM channel. Therefore, optimal system configurations are ones in which the request link bus and response link bus do not negatively impact the DRAM efficiency. The width and speed of these buses should be configured such that request and response packets can be sent at a rate that does not stall the DRAM, either due to a lack of available requests issuable to the DRAM or due to an inability to clear the read return queue quickly enough.

As previously mentioned, the response link bus is responsible for removing response packets from the read return queue. The fastest rate at which data from the DRAM can be added to this queue is determined by the burst length (BL) and tFAW DRAM timing constraints (Figure 23). As described above, it is possible to calculate a first-order approximation for the necessary response link bus bandwidth when taking into account the DRAM's tFAW (37.5ns for DDR3-1066 and 30ns for DDR3-1333 and DDR3-1600) and BL values (7.5ns for DDR3-1066, 6ns for DDR3-1333, 5ns for DDR3-1600). This calculation can be seen in Equation 1 and dictates

how quickly the response link bus must transmit four requests in order to prevent stalling the DRAM due to lack of space in the read return queue.

$$TimeToTransmit = \frac{BL}{2} \times 4 \times tCK + tRTRS \times tCK \tag{1}$$

This equation represents the length of time between the start of the longest possible continuous data burst and the next possible chance for new data to arrive from the DRAM (situation depicted in **Figure 23**). The first term  $(BL/2 \times 4 \times tCK)$  is the total time (in nanoseconds) that these four continuous data bursts take to be retrieved from the DRAM. The second term  $(tRTRS \times tCK)$  is the time (in nanoseconds) that it takes to switch between transmission sources – in this case, separate ranks attached to the DRAM bus. When these terms are summed, the result represents the period of time in which the greatest quantity of continuous data can return in the shortest amount of time. This is solely a result of the tFAW timing constraint.

If the response link bus bandwidth is capable of transmitting four response packets within this computed time, then, from the DRAM's perspective, it would be impossible to stall as a result of the return queue being full. Other parts of the system may have an impact on this and will be explored in later sections. The length of time to send a single 72B response packet for numerous response link bus configurations can be seen in **Table 1**. When relating these values to the times computed with **Equation 1**, it is clear that certain response link bus configurations would not be able to remove response packets from the read return queue fast enough to prevent it from reaching maximum capacity and thus causing the DRAM to stall.

| Data Lanes | $3.2~\mathrm{GHz}$ | 6.4 GHz    | 9.2 GHz   |

|------------|--------------------|------------|-----------|

| 4          | 22.5  ns           | 11.25 ns   | 7.5 ns    |

| 8          | 11.25  ns          | 5.625  ns  | 3.75  ns  |

| 12         | $7.5  \mathrm{ns}$ | 3.75  ns   | 2.5 ns    |

| 16         | 5.625  ns          | 2.8125  ns | 1.875  ns |

Table 1: Time to transmit response packet over response link bus

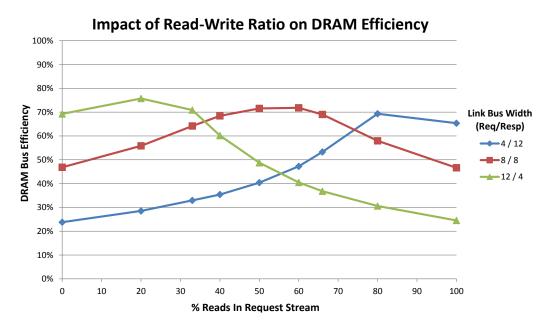

The request link bus width and speed will have an impact on the DRAM efficiency as well. In a BOB memory system, the request link bus is responsible for issuing read request packets (8 bytes) and write request packets (8 bytes of overhead and 64 bytes of data) to their respective simple controllers. The request link bus must be able to send these packets at a rate which keeps the DRAM as busy as possible. When a simple controller's work queue is full, the issuing logic is more likely to find a command which can be issued within the timing constraints imposed by the DRAM.

An accepted rule-of-thumb is that a typical request stream will have a read-to-write request ratio of approximately 2-to-1. Implemented systems have accounted for this fact by weighting response paths more than requests paths. This can be seen starting from the FB-DIMM standard, which had the northbound bus (for responses) 40% larger than the southbound bus (for requests) [9]. The new architectures detailed above adopt this convention as well with Intel's SMI response bus 33% larger [13] than the request bus, and IBM's Power7 system whose response bus is twice as wide as the request bus [12].

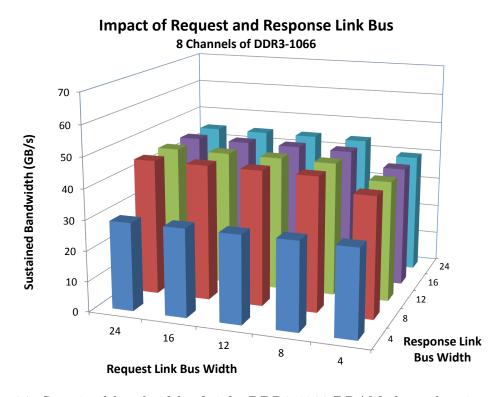

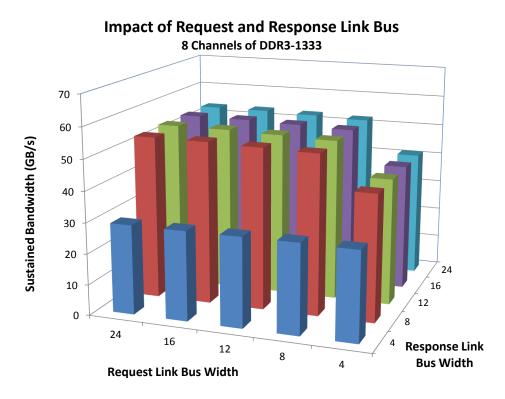

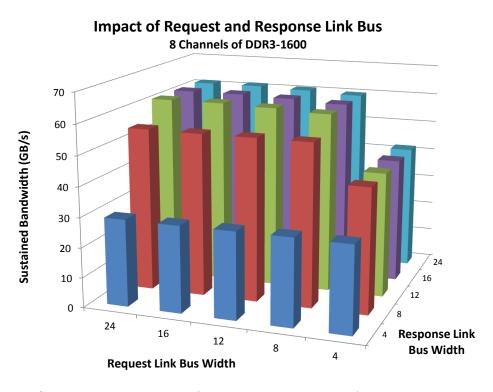

Limit-case simulations are performed with eight DRAM channels of various speed grades that are attached to different request and response link bus configurations (operating at 3.2 GHz). The results can be seen in **Figures 24, 25, & 26**. The

simulation results show a clear peak bandwidth where additional link bus bandwidth has no impact on the overall performance. This is due to the link bus bandwidth exceeding that which is required by the DRAM to reach its maximum attainable efficiency.

Figure 24: Sustained bandwidth of eight DDR3-1066 DRAM channels using various link bus configurations

Figure 25: Sustained bandwidth of eight DDR3-1333 DRAM channels using various link bus configurations

Figure 26: Sustained bandwidth of eight DDR3-1600 DRAM channels using various link bus configurations