**Bruce Jacob**

University of Maryland

SLIDE 1

# A Holistic Approach to DRAM

#### **Prof. Bruce Jacob**

**Electrical & Computer Engineering University of Maryland, College Park**

#### **OUTLINE**

- Anecdotes, Vision

- Our Past & Present Work

- Anecdotes Revisited

- Conclusions

**Bruce Jacob**

University of Maryland

SLIDE 2

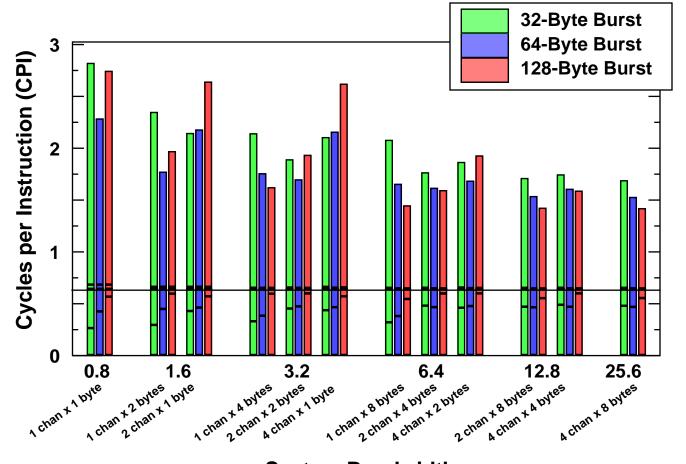

# **Anecdote I: System Issues**

System Bandwidth (GB/s = Channels \* Width \* 800MHz)

Benchmark = GCC (SPEC 2000), 2 banks/channel

Bruce Jacob

University of Maryland

SLIDE 3

**Bruce Jacob**

University of Maryland

SLIDE 4

**Bruce Jacob**

University of Maryland

SLIDE 5

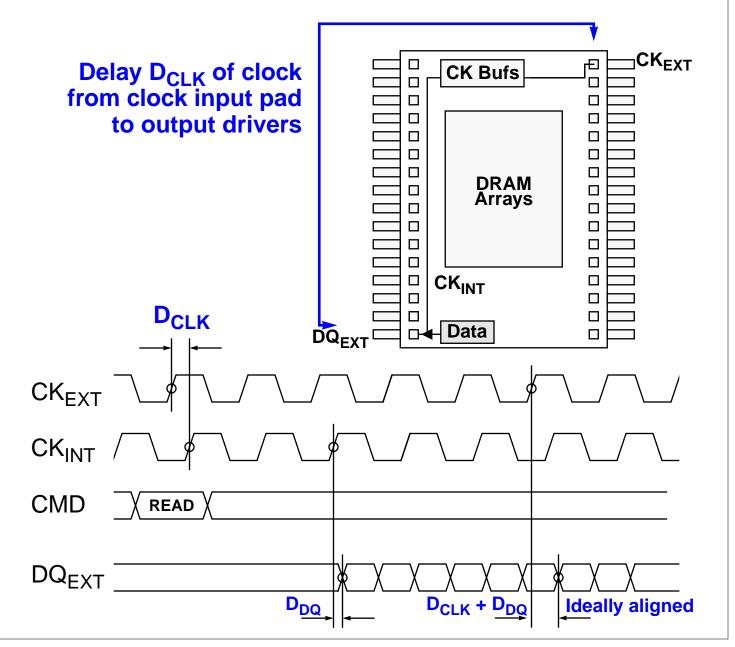

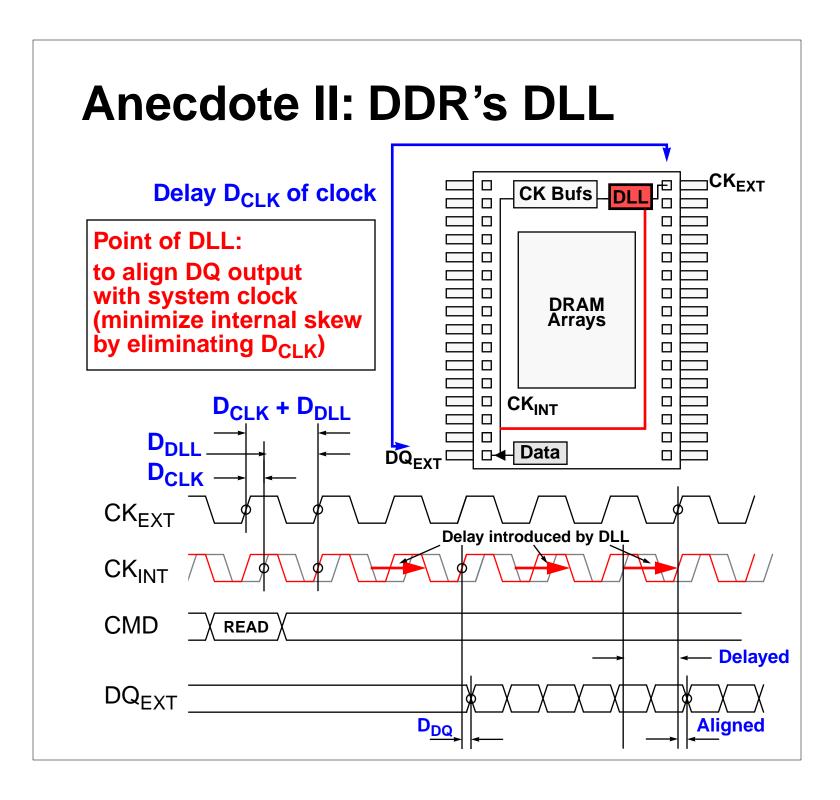

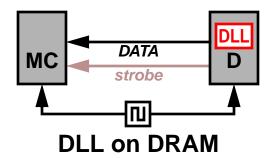

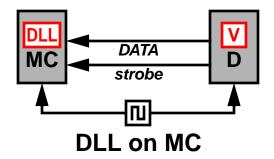

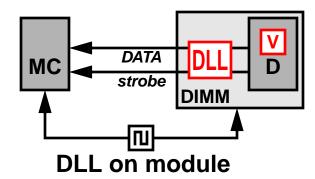

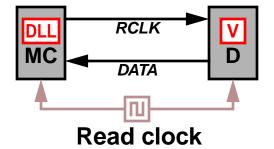

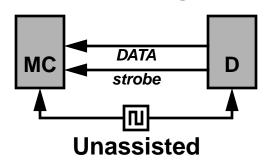

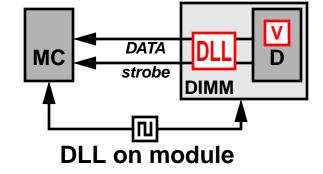

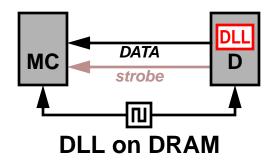

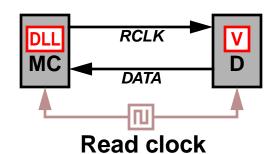

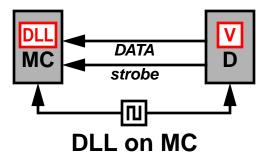

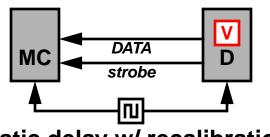

### Anecdote II: DDR's DLL

#### A handful of alternatives:

**Bruce Jacob**

University of Maryland

SLIDE 6

# Anecdote III: Circuit v System

#### **t<sub>DQS</sub>** limitations:

Bruce Jacob

University of Maryland

SLIDE 7

### **Vision**

Must make circuit-level decisions considering system-level ramifications

(holistic approach)

**Bruce Jacob**

University of Maryland

SLIDE 8

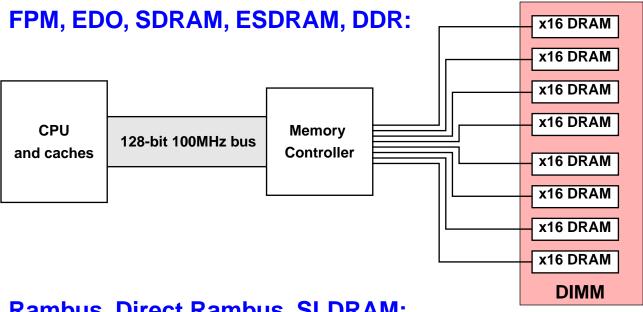

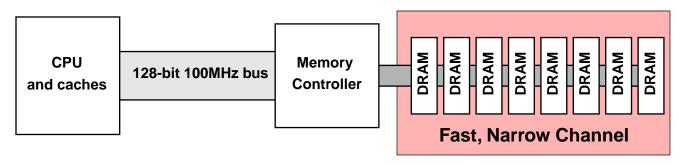

### **Past Work: Device-Level**

#### Rambus, Direct Rambus, SLDRAM:

[Cuppu et al. ISCA 1999]

**Bruce Jacob**

University of Maryland

SLIDE 9

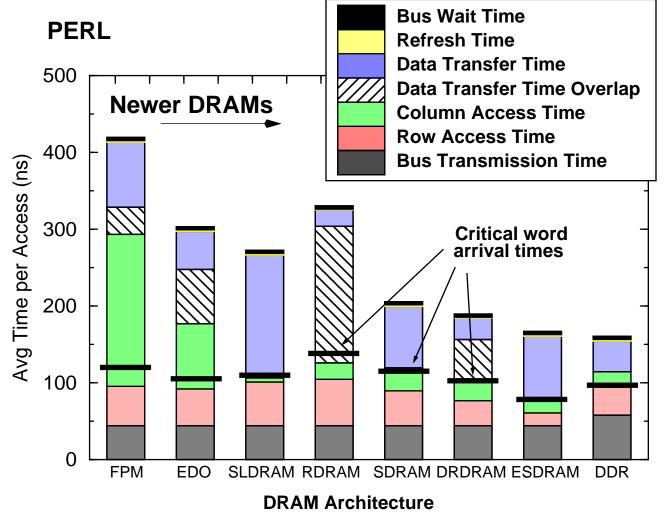

### **Past Work: Device-Level**

#### **Average Latencies**

[Cuppu et al. ISCA 1999]

**Bruce Jacob**

University of Maryland

SLIDE 10

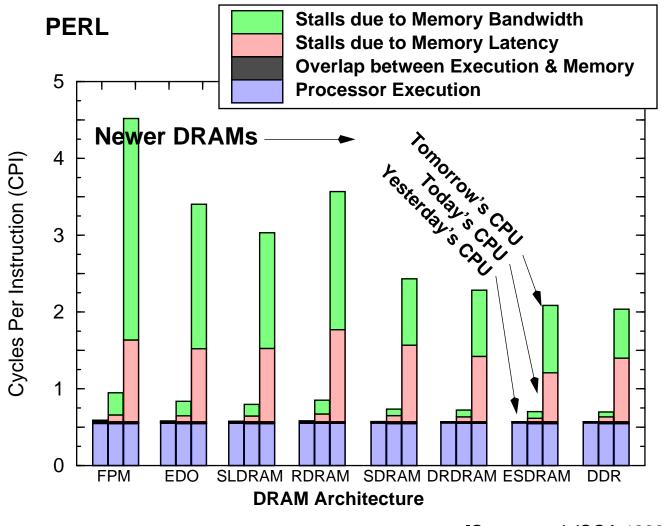

### **Past Work: Device-Level**

#### **Bandwidth-Enhancing Techniques I:**

[Cuppu et al. ISCA 1999]

**Bruce Jacob**

University of Maryland

SLIDE 11

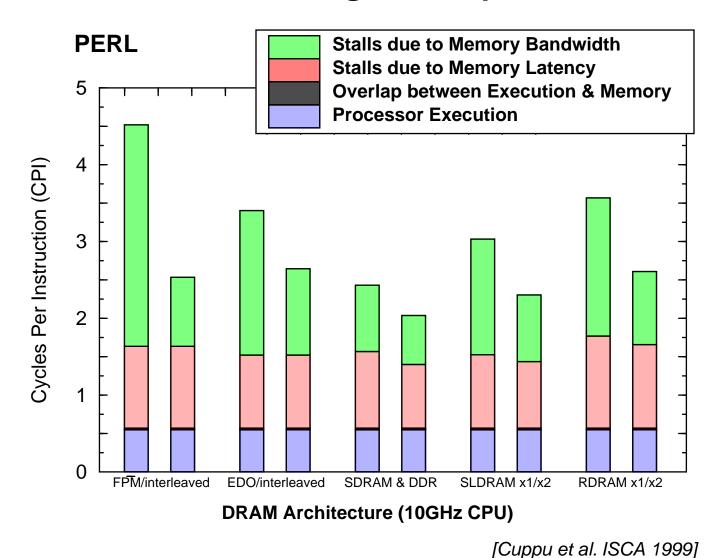

### **Past Work: Device-Level**

#### **Bandwidth-Enhancing Techniques II:**

**Bruce Jacob**

University of Maryland

SLIDE 12

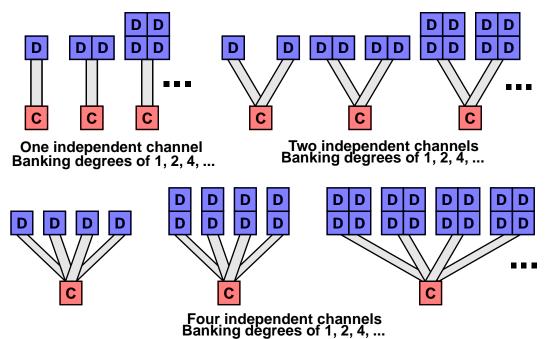

# Past Work: System-Level

#### Even when we restrict our focus ...

1, 2, 4 800 MHz Channels

8, 16, 32, 64 Data Bits per Channel

1, 2, 4, 8 Banks per Channel (Indep.)

32, 64, 128 Bytes per Burst

[Cuppu & Jacob ISCA 2001]

**Bruce Jacob**

University of Maryland

SLIDE 13

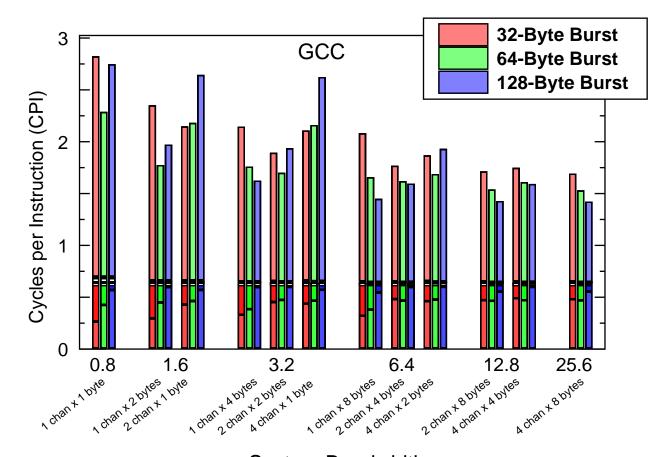

# Past Work: System-Level

... the design space is FAR from regular ...

System Bandwidth (GB/s = Channels \* Width \* 800MHz)

[Cuppu & Jacob ISCA 2001]

**Bruce Jacob**

University of Maryland

SLIDE 14

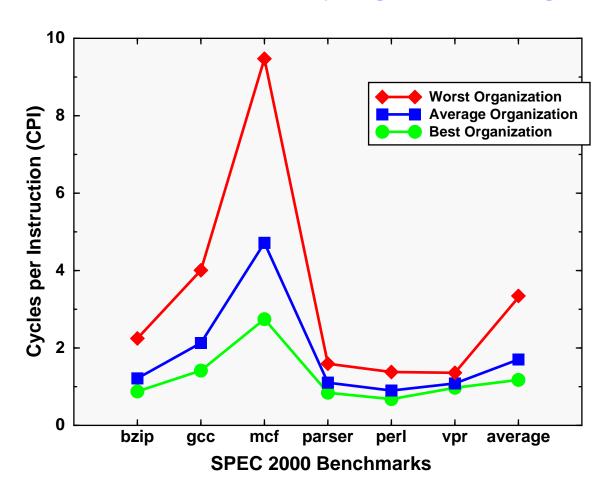

# Past Work: System-Level

... and the cost of poor judgment is high.

[Cuppu & Jacob ISCA 2001]

**Bruce Jacob**

University of Maryland

SLIDE 15

### An Aside

Past work used first-order models.

Present work uses models accurate to second & third order effects ...

**Bruce Jacob**

University of Maryland

SLIDE 16

### [ Definition: Zero'th Order ]

```

if ( INSTR.is_loadstore ) {

if (L1_cache_miss( INSTR.daddr )) {

if (L2_cache_miss( INSTR.daddr )) {

cycles += DRAM LATENCY;

OR

INSTR.ready = now() + DRAM LATENCY;

```

**Bruce Jacob**

University of Maryland

SLIDE 17

### An Aside

Past work used first-order models.

Present work uses models accurate to second & third order effects ...

**Bruce Jacob**

University of Maryland

SLIDE 18

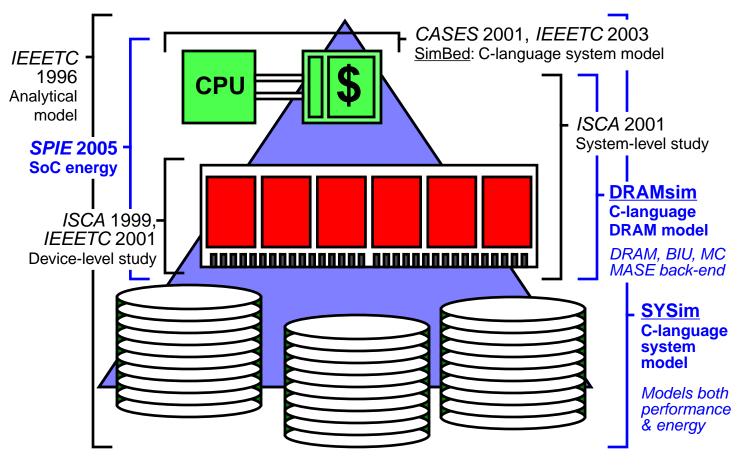

### **Past & Present Work**

IEEETC 1996: System-level analytical tool for cost/performance

ISCA 1999, IEEETC 2001: DRAM device-level characterization

CASES 2001, IEEETC 2003: Performance & energy modeling of CPU and SRAM

(model executes unmodified RTOS)

ISCA 2001: DRAM system-level characterization

SPIE 2005: SystemC modeling of energy in systems-on-chip

**Bruce Jacob**

University of Maryland

SLIDE 19

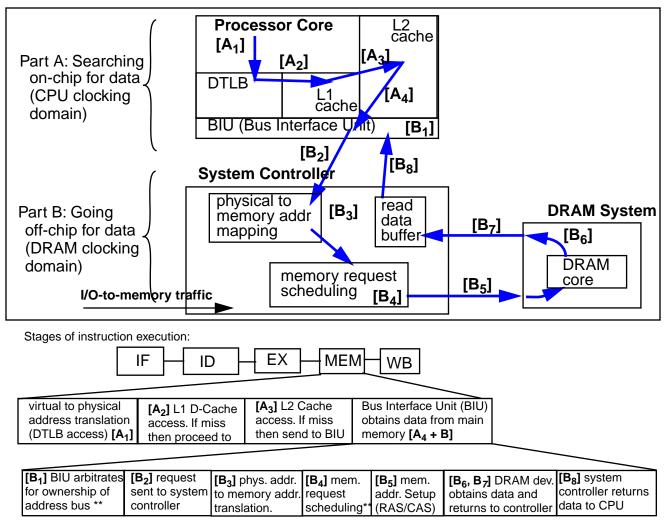

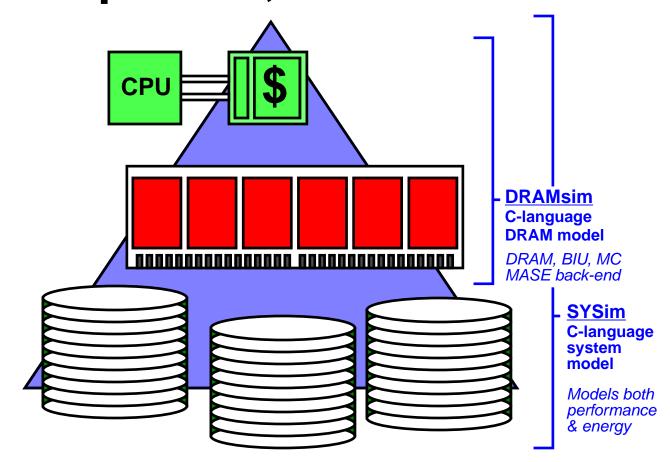

### **Present Work: DRAMsim**

#### **Execution of a Load Instruction**

<sup>\*\*</sup> Steps not required for some processor/system controllers. protocol dependant.

**Bruce Jacob**

University of Maryland

SLIDE 20

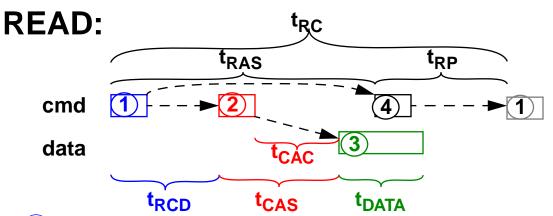

### **Present Work: DRAMsim**

- 1 Active: Open Row, t<sub>RCD</sub> time later, a CAS command may be issued to the DRAM chip

- CAS: Column Read command, t<sub>CAS</sub> time later, data begins to be placed onto the Data bus. We use t<sub>CAC</sub> to factor out command transmission time.

- (3) Data: The number of cycles that the data transmits over the Data bus

- Precharge: Close the Row, this command may be issued t<sub>RAS</sub> time after the Active command. After t<sub>RP</sub> time, another active command may be issued.

- 2 CWD: Column Write Delay, the number of cycles that the controllers must wait before placing the data onto the data bus.

- (5) RTR: Retirement delay, this is for systems with write delay buffers.(RDRAM)

**Bruce Jacob**

University of Maryland

SLIDE 21

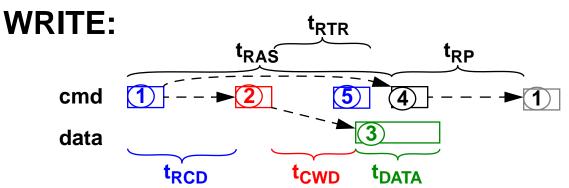

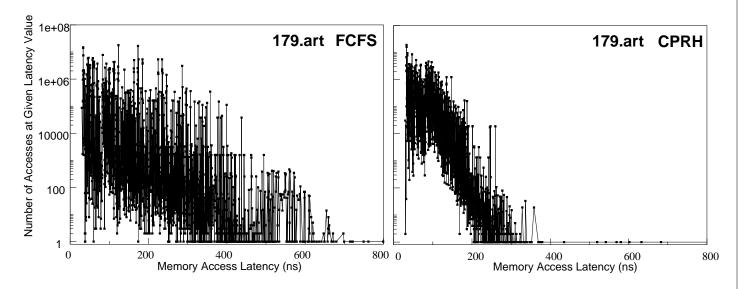

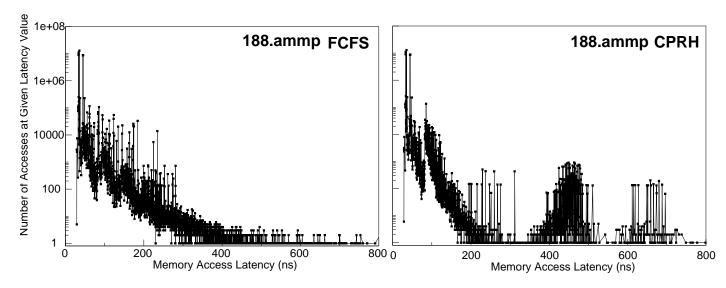

### **Present Work: DRAMsim**

#### **Memory Access Latency Distribution**

**Bruce Jacob**

University of Maryland

SLIDE 22

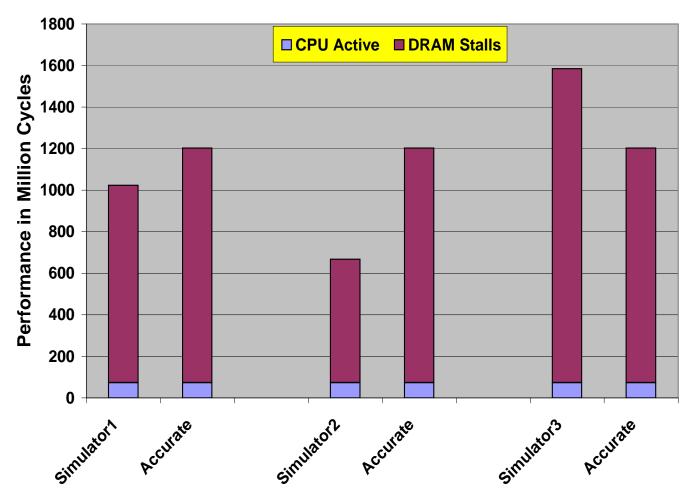

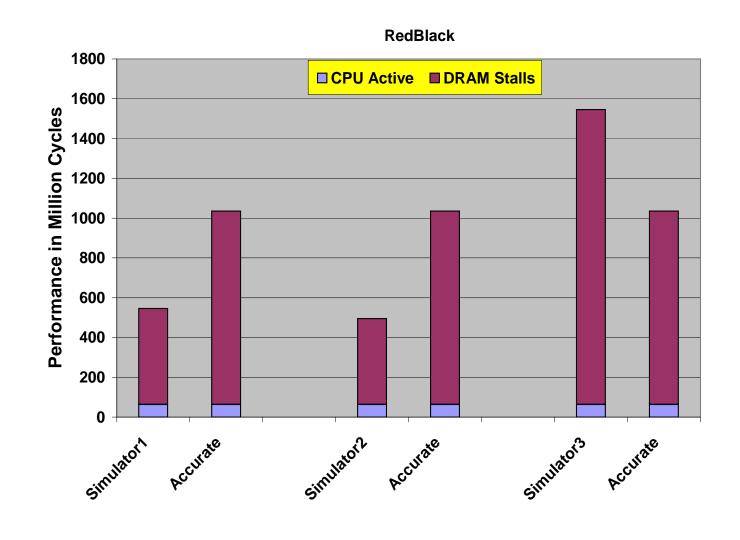

# Present Work: Why?

#### Benefit: Performance Numbers (DRAMsim)

**Bruce Jacob**

University of Maryland

SLIDE 23

# Present Work: Why?

#### Benefit: Performance Numbers (DRAMsim)

**Bruce Jacob**

University of Maryland

SLIDE 24

# Present Work: Why?

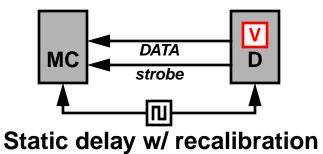

Benefit: Insights (Anecdote II, revisited)

Static delay w/ recalibration

Bruce Jacob

University of Maryland

SLIDE 25

# Present Work: Why?

Benefit: Insights (Anecdote II, revisited)

| SCHEME      | COST             | EFFECTI              | VENES  | SS (Und | ertainty | in read) |

|-------------|------------------|----------------------|--------|---------|----------|----------|

| No DLL      | 0                | D <sub>CLK</sub> + X | (mit + | wire +  | Recv +   | Clk skew |

| on DRAM     | 16xDLL           | ×                    | (mit + | wire +  | Recv +   | Clk skew |

| on MC       | 2xDLL<br>16xVern |                      |        | wire +  | Recv     |          |

| on DIMM     | 2xDLL<br>16xVern |                      |        | wire +  | Recv +   | Clk skew |

| Read<br>CLK | 2xDLL<br>16xVern |                      |        | wire +  | Recv     |          |

| Static      | 16xVern          | ×                    | (mit + | wire +  | Recv     |          |

- Cost = for 2-DIMM system, 8 DRAM parts per DIMM note: "cost" applies to both die area and power

- Uncertainty = *very rough, intuitive idea*

**Bruce Jacob**

University of Maryland

SLIDE 26

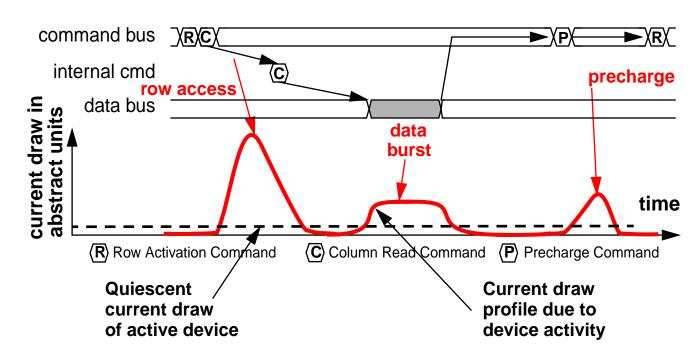

## Anecdote III, revisited

#### Power consumption in DRAM devices:

- Row activation, data read-out, bank precharge: all are relatively expensive operations

- Current draw of operation additive to quiescent value

#### ... So what's the big deal?

**Bruce Jacob**

University of Maryland

SLIDE 27

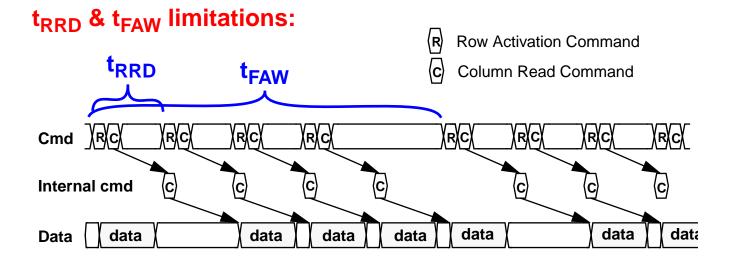

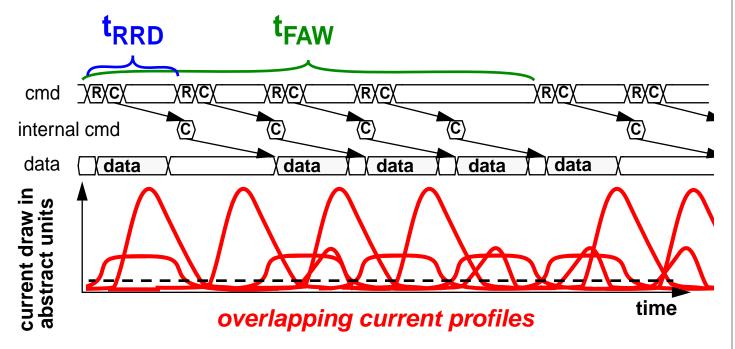

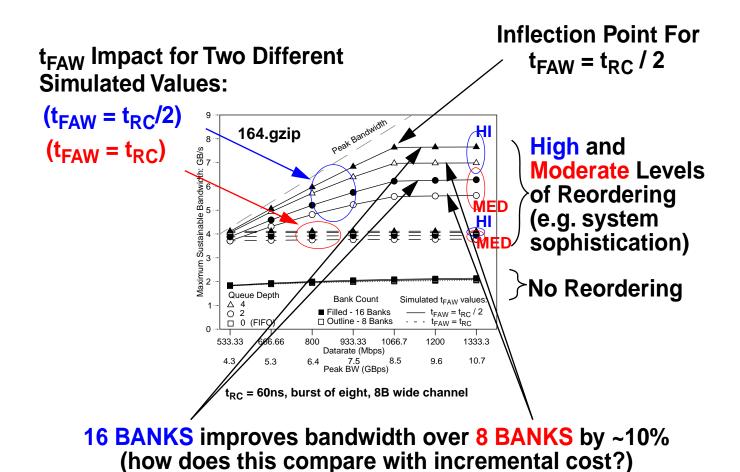

## Anecdote III, revisited

t<sub>RRD</sub> & t<sub>FAW</sub> protocol-level limitations placed upon device to limit maximum current draw

- Severely limits bus efficiency from single rank

- Problem worsens in future: parameters defined in nanoseconds, not cycles

**Bruce Jacob**

University of Maryland

SLIDE 28

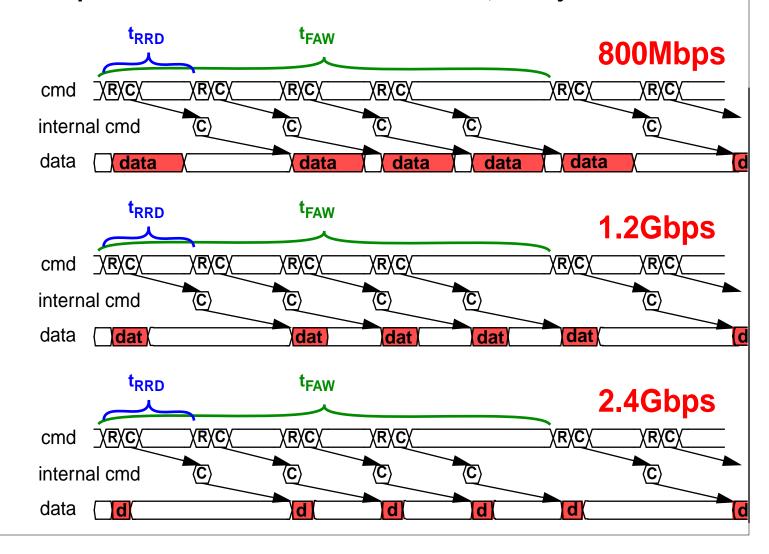

### Anecdote III, revisited

t<sub>RRD</sub> & t<sub>FAW</sub> — Problem worsens in future: parameters defined in *nanoseconds*, not *cycles*

**Bruce Jacob**

University of Maryland

SLIDE 29

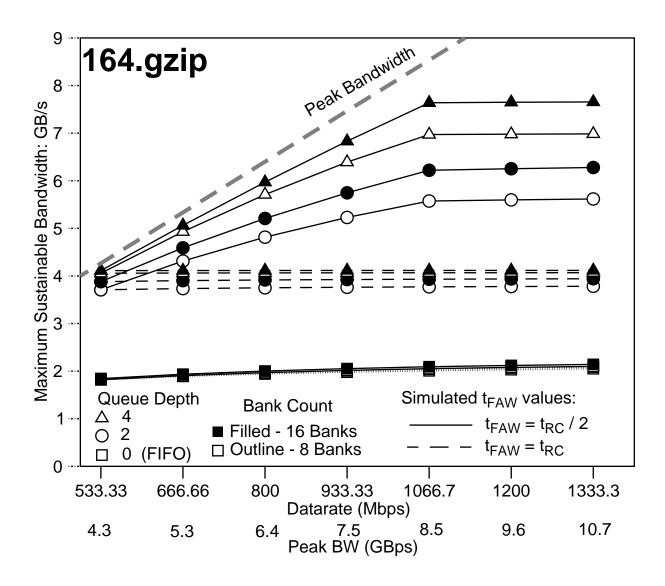

### Max. Sustainable Bandwidth

t<sub>RC</sub> = 60ns, burst of eight, 8B wide channel

**Bruce Jacob**

University of Maryland

SLIDE 30

### Max. Sustainable Bandwidth

**Bruce Jacob**

University of Maryland

SLIDE 31

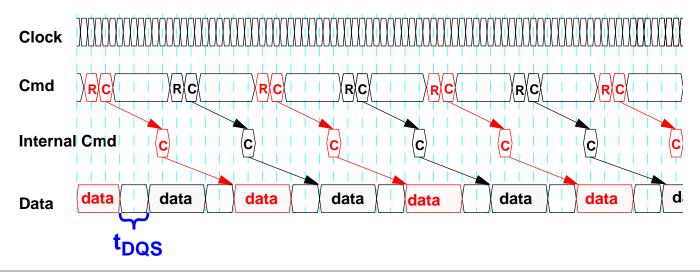

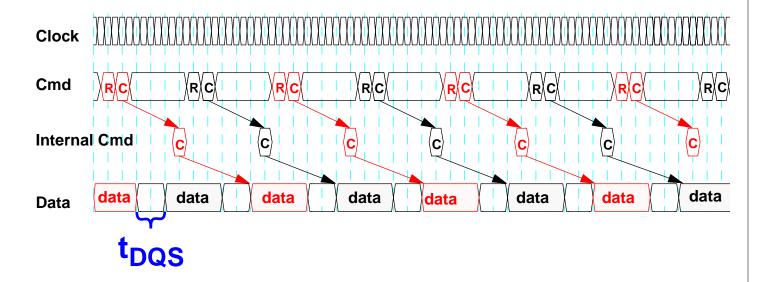

### But Wait, There's More ...

t<sub>DQS</sub> protocol-level limitation placed upon ranks to prevent data-bus collisions on rank hand-off

- Severely limits bus efficiency from multiple ranks

- Luckily, it is defined in cycles and not nanoseconds

**Bruce Jacob**

University of Maryland

SLIDE 32

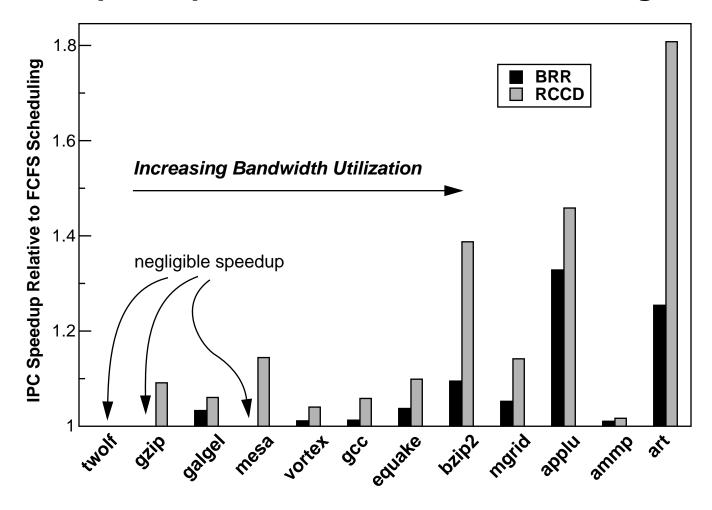

# Solution I: Scheduling

Problems created by t<sub>FAW</sub> + t<sub>RRD</sub> + t<sub>DQS</sub>

t<sub>FAW</sub> + t<sub>RRD</sub>

**Must spread out ACT commands**

• t<sub>DQS</sub>

Must switch ranks infrequently

Salient point: t<sub>FAW</sub> does not place limit on total number of open banks

Problem can be solved with scheduling: row-column command decoupling (RCCD)

- Schedule ACT commands far before their corresponding READ commands

- Schedule large number of bank-reads before switching ranks

[patent pending]

**Bruce Jacob**

University of Maryland

SLIDE 33

# Solution I: Scheduling

#### IPC Speedup Relative to FCFS Scheduling

**Bruce Jacob**

University of Maryland

SLIDE 34

# Solution I: Scheduling

**Bruce Jacob**

University of Maryland

SLIDE 35

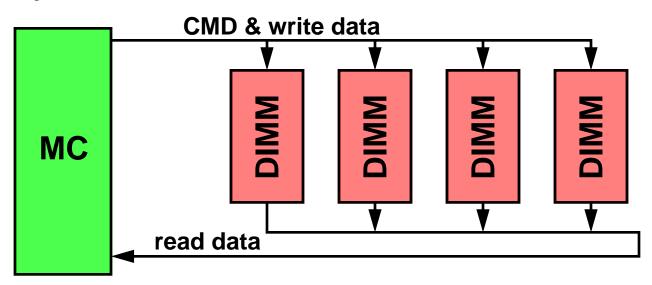

# Solution II: Topology, etc.

### Problems solved by $t_{FAW} + t_{RRD} + t_{DQS}$

t<sub>FAW</sub> + t<sub>RRD</sub>

Instantaneous current draw in device

t<sub>DQS</sub> Bus collisions on rank handoffs

#### Any alternative solution will do ...

- Topology eliminates collisions (can account for static DIMM-DIMM skew with Vernier-type solution)

- Note: solution requires source-synchronous clocking

**Bruce Jacob**

University of Maryland

SLIDE 36

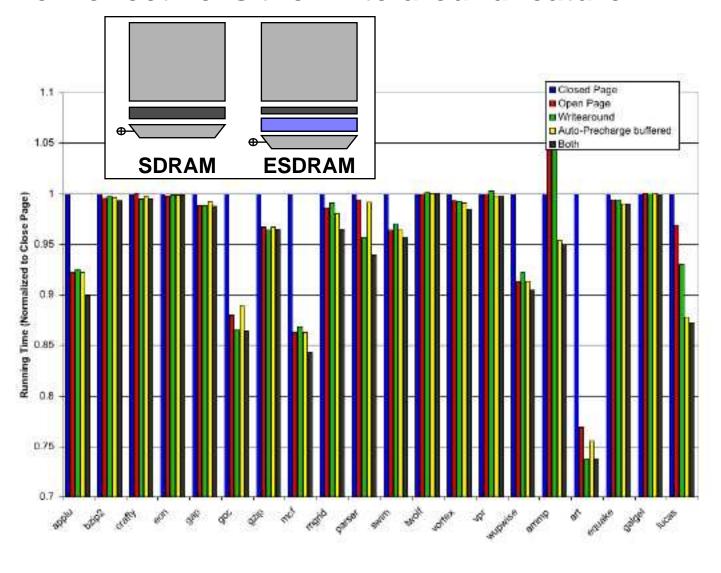

# Other Items, e.g. ESDRAM

How effective is the write-around feature?

**Bruce Jacob**

University of Maryland

SLIDE 37

## Perspective, Future Work

- Investigating these types of issues (local-vs-system) at all levels of the hierarchy (cache, disk, etc).

- MKP book to come ("holistic approach" ??)

- Goal: <u>SYSim</u> will be open-source release w/ book

**Bruce Jacob**

University of Maryland

SLIDE 38

# **Summary**

No longer appropriate to optimize subsystems in isolation: local optima do not yield globally optimal system

Systemic behaviors: unanticipated interactions yielding inefficiencies

#### **Specific instances:**

- t<sub>FAW</sub> + t<sub>RRD</sub> + t<sub>DQS</sub> severely limits BW

- Choice of DLL on DDR SDRAMs to de-skew parts

Many problems can be addressed by system-level solutions; can be better than circuit-level solutions

**Bruce Jacob**

University of Maryland

SLIDE 39

### **Et Cetera**

#### **MEMORY-SYSTEMS RESEARCH SUPPORT:**

- NSF (CAREER Award)

- Intel

- Cray

#### (CURRENT) MEMSYS GRAD STUDENTS:

- Dave Wang: DRAMsim, t<sub>FAW</sub> + t<sub>RRD</sub> + t<sub>DQS</sub> studies, etc.

- Ankush Varma: SystemC system-on-chip energy model

- Nuengwong Tuaycharoen: SYSim development

- **Sean Leventhal:** Other studies (e.g. ESDRAM, MC, etc.)

#### **CONTACT INFO:**

- Prof. Bruce Jacob

ECE Dept., University of Maryland, College Park, MD

- http://www.ece.umd.edu/~blj/blj@umd.edu